# RF Energy Harvesting for Embedded Systems: A Survey of Tradeoffs and Methodology

Tolga Soyata, Lucian Copeland, and Wendi Heinzelman

### Abstract

This paper presents an overview of passive Radio Frequency (RF) energy reception and power harvesting circuits for isolated communications and computing systems lacking access to primary power sources. A unified understanding of the energy harvesting alternatives is provided, followed by an elaborate study of RF energy harvesting within the context of embedded systems. A detailed discussion of RF technologies ranging from the directed communications signal reception to dispersed ambient power harvesting is provided. A comparative focus on design tradeoffs and process alterations is provided to represent the diversity in the applications requiring wireless RF harvesting units. Also included is an analysis of system combinations, and how wake up units, active storage, and duty cycling play roles in the consumption and harvesting of RF energy.

Digital Object Identifier 10.1109/MCAS.2015.2510198 Date of publication: 12 February 2016

### I. Introduction

ith the surge of low power embedded systems in consumer and commercial use, there has been a similar boom in research directed towards improving the power efficiency for these systems. When considering devices designed for applications such as supply chain management and the Internet of Things (IoT), using wireless power transmission over traditional bandwidths has become an appealing prospect for reducing cost and the need for periodic maintenance. At mid-range distances in the tens of meters and legally permissible power levels, ultra-high frequency (UHF) power transmission may be a sufficient replacement for a battery or other external power source, allowing for periodic ultra-low-power  $(1-100\,\mu\text{W})$  data processing and signal interpretation without the need for

an internal power supply. Bypassing the need for chemical power sources or "active listening" for incoming signals, passive systems with wireless power converters are capable of functioning for many times the lifespans of their constantly-active counterparts.

However, the wireless embedded systems field is characterized by diversity in the application requirements and a corresponding diversity in design philosophy. The differences between applications preclude the concept of a "universal" approach to the design of low power receivers, and require that every circuit must be considered separately to retain the efficiency, range, and cost required by their application. Thus, the design of wireless harvesting units must be characterized through critical tradeoffs, which can then be used by the designer to create the optimal circuit for a given application.

This paper presents a survey of these tradeoffs for the technologies used in UHF band wireless power harvesting. Given that extensive surveys of comparative efficiencies [1] and networking protocols [2] already exist, our analysis will focus specifically on the varying circuit structures for LC matching, rectification, digital processing, and tradeoffs in modulation/demolation choices along with appropriate results indicating the benefits and drawbacks of published models, theorems, and implementations.

Tolga Soyata, Lucian Copeland, and Wendi Heinzelman are with Dept. of Electrical and Computer Engineering, University of Rochester, Rochester, NY 14627, {soyata, lcopeland2, wheinzel}@ece.rochester.edu.

| Table 1.<br>Operational frequency range of solar panels. |         |             |                    |  |  |  |

|----------------------------------------------------------|---------|-------------|--------------------|--|--|--|

| Frequency                                                | Band    | Notes       | λ                  |  |  |  |

| 270 THz                                                  | IR      | Infrared    | $1.1\mu\mathrm{m}$ |  |  |  |

| 430 THz                                                  | Visible | Red         | 700 nm             |  |  |  |

|                                                          | Visible |             |                    |  |  |  |

| 790 THz                                                  | Visible | Violet      | 380 nm             |  |  |  |

| 1.6 PHz                                                  | UV      | Ultraviolet | 200 nm             |  |  |  |

The rest of this paper is organized as follows: Section II details and compares energy harvesting alternatives. Section III introduces the content of the survey with a summary of motivating applications for RF energy harvesting and the design tradeoffs for these applications. The background sections IV, V, and VI introduce important context for the transmission of wireless RF power and the evaluation metrics for doing so and a stage model of the RF power harvester/communications circuit. The analysis portion of the paper is contained in sections VII, VIII, IX, and X. These sections cover RF power harvester design tradeoffs for impedance matching, rectification and voltage multiplication, power management, and communications, respectively. Section XI compares these various tradeoffs for reference, and Section XII concludes our findings. Appendix A provides a glossary of the abbreviations used throughout the paper along with references to the corresponding section where they are described.

### **II. Energy Harvesting Alternatives**

In this section, we provide a unified understanding of energy harvesting and list the available energy sources and their characteristics.

### A. Unifying the Understanding of Energy Sources

In general, *energy* is transported through the ability of "matter" or "waves" to carry a *force* within a medium such as water, air, or a solid material such as a metal. In energy harvesting, the ultimate goal is to intercept this transported force and convert it to electrical energy. This is achieved by applying the transported force to a

**Figure 1.** Three different solar panels: 1.5 W, 10 W, and 30 W. A coin is placed on the panels to allow comparison of relative and absolute sizes.

transducer (e.g., a wind turbine), that transfers the force into the electrons in a circuit (via increased potential energy), thereby facilitating an electric current.

Depending on "what" originates and transports the force and which medium is used during transportation, energy sources can be broken down into two primary categories:

**Mechanical Waves:** Imagine a wind starting at some point on earth. The source of this movement is some atmospheric event that pushes the air in a certain direction. Since the air is made mostly of N<sub>2</sub> and O<sub>2</sub> molecules, pushing one atom (e.g., "O" within the O2 molecule) against another will repel the destination atom. This will transfer the momentum of one atom to the next one, thereby moving that atom (and its covalent-bonded neighbor atom, hence the entire O<sub>2</sub> molecule) in approximately the same direction. According to conservation of momentum [3], some energy loss is expected due to some heating on either atom and due the bounce-back of the initial atom, potentially hitting another atom somewhere else. The net effect is that, the air moves and the force is transported from one atom to another through the medium (i.e., the air).

An analogy is a billiard table in which an initial billiard ball is thrown against another. The force is transported from one billiard ball to another based on the law of conservation of momentum. The transportation of the force continues until the final billiard ball is intercepted by one of the holes on the table (i.e., harvested). The intercepted billiard ball carries a force that is proportional to the very first billiard ball. This type of a force-carrying mechanism through "atom-pushing waves" is termed mechanical waves or compressional waves. Wind energy, sound energy, and vibration energy are transported through mechanical waves. They are harvested by using wind turbines, microphones, and piezo crystals as transducers.

**Electromagnetic Waves:** Imagine a valence electron losing energy and moving from a higher-energy state to a lower-energy state at some point on earth. Where will the lost energy go? According to the conservation of energy [3], it will radiate as a photon at the frequency determined by

$$E = h\nu = \frac{hc}{\lambda} \tag{1}$$

where  $\nu$  is the frequency at which the photon is oscillating, corresponding to the wavelength  $\lambda$ . h is the Planck constant and can be thought of as being the energy that the photon carries *per cycle of oscillation*. This photon can continue its travel indefinitely until it encounters an atom (more specifically, an electron) along its path. When it hits an electron, if the electron can absorb the energy that the photon is carrying according to Eq. 1, it

When considering devices designed for applications such as supply chain management and the Internet of Things (IoT), using wireless power transmission over traditional bandwidths has become an appealing prospect for reducing cost and the need for periodic maintenance.

will become more energetic and will move from valence band to conduction band. Therefore, the force that the photon carries is transferred to the electron, and the photon vanishes.

The type of waves created by photons is defined as *electromagnetic waves* for which the medium can be any solid, liquid, or gas. Solar energy and RF energy are transported through electromagnetic waves. The transducers that can turn these electromagnetic waves into energy are the photo-diodes in solar panels and inductors, respectively.

### B. Wind, Sound, and Vibration Energy Harvesting

To harvest wind energy, an electric motor is used, that contains a magnetic rotor. This setup facilitates the conversion of the mechanical energy of the wind into the rotation of the motor, which induces an electromagnetic force (EMF) on the rotor. This EMF is the harvested energy in the form of an electrical current. Although small scale turbines are available for embedded circuits [4], that produce a power output in the mW range, this is much less common than the large wind turbines designed to produce power outputs in the kW range [5].

In theory, sound energy can be harvested by using a microphone, though this is not as common. Vibration energy harvesting, on the other hand, is a viable alternative to provide power for sensors in areas that have sufficient vibration activity. Examples include seismic activity areas, subways, cars, industrial machinery, and raindrops on tree leaves. Commonly used transducers include piezoelectric and magneto-strictive materials [6]. The amount of harvested power is expected to be in the multiple- $100\,\mu\mathrm{W}$  range for this type of energy harvesting.

### C. Solar Energy Harvesting

In solar energy harvesting, the source of the energy is the photons that the sun generates during the nuclear reactions inside the sun. These photons travel from the sun to the earth in the form of electromagnetic waves and are intercepted by solar panels that turn photons into electrical energy. Table 1 shows the frequency band of the photons that solar panels can harvest. In additions to the entire visible light spectrum, solar panels can harvest the photons in a small UV and IR band as well.

Solar panels are made out of photo-diodes that have an exposed junction for the photons to hit. When a photon hits an electron of the Si atom within the photo-diode, it can move a Si valance electron from valance to conduction and give it sufficient energy to cross the PN junction. Therefore, the energy that the photon carries is converted to electrical energy. Figure 1 shows three different solar panels that can harvest output power levels of 1.5 W, 10 W, and 30 W. Their sizes are  $3.5^{\circ}\times5^{\circ}$ ,  $9.5^{\circ}\times13.5^{\circ}$ , and  $14^{\circ}\times26.5^{\circ}$ , respectively. Their total surface area is  $0.011~\text{m}^2$ ,  $0.083~\text{m}^2$ , and  $0.24~\text{m}^2$ . The power output per unit area of these solar panels can be calculated as  $130-140~\text{W/m}^2$ .

### D. RF Energy Harvesting

Radio frequency (RF) waves are electromagnetic waves that originate at a transmitter in the form of a photon that is oscillating within one of the pre-determined transmission frequency bands such as UHF, SHF, or VHF, etc. Note the difference between RF and solar harvesting: In RF harvesting, the source is an *intentional electromagnetic radiation by an electronic device*, rather than the *natural radiation by the sun*. The most important consequence of this fact is that, the electromagnetic properties of the RF radiation can be determined by the transmitter.

RF transmission frequencies (e.g., UHF ranging from 300 MHz to 3 GHz) are substantially lower than the frequency of the photons hitting solar panels (270 THz–1600 THz), translating to a 5–6 orders-of-magnitude lower energy-per-photon for RF harvesting as compared to solar, according to Eq. 1. This very fact drastically limits the applicability of the RF harvesting to extremely small embedded systems.

### E. RF Energy Harvesting for Embedded Systems

The primary focus of this paper is RF energy harvesting for embedded systems. Comparing solar and RF harvesting, we notice that the harvested power levels are consistent with photon transmission frequency (i.e., 4–5 orders-of-magnitude lower for RF per m<sup>2</sup>). Despite this seemingly big disadvantage of RF power levels, RF harvesting is still a very useful and practical alternative for the following reasons:

Passive RF circuits can function at 2–100  $\mu$ W due to the ability of the state-of-the-art VLSI technology to

25

- incorporate non-trivial circuit functionality within such a power envelope.

- Since the goal of an embedded RF system is to provide a highly specific and limited set of tasks, Application Specific Integrated Circuits (ASICs) are designed for these specific tasks that could achieve orders-of-magnitude power advantages as compared to generic circuits.

- Since RF energy can travel within materials such as water, plastic, matte glass, paper, etc., RF embedded systems can be placed in areas where there is no solar power or "exposed" sensory outlet. In such scenarios, RF power harvesting might be the only alternative.

- Backscattering communication allows a passive RF circuit to communicate with the transmitter (i.e., the interrogator) using a " μW" power source, thereby eliminating the need for a "mW" power source within the embedded circuit that would be necessary for active RF communication [7].

- Directed communication using "light energy" is possible between a source and an embedded system by using a laser beam. The receiver can simply use solar panels to intercept and harvest this energy. In fact, the amount of energy a laser beam can transmit is substantially higher than that of an RF antenna. However, directed communication using light energy has very limited use due to the implied hazards on the eyes of humans and other animals. For directed (i.e., dedicated-source) communication, RF is the most widely-accepted alternative.

RF harvesting can be broken down into two major categories:

Ambient RF Energy Harvesting: Passive harvesting systems may take advantage of local ambient RF energy to charge much larger power storage systems over extended or indefinite periods of time [8]–[10]. This ambient energy may come in the form of Wi-Fi, TV, or military broadcasting [11], as well as directed energy transmission. A typical ambient RF harvesting circuit is

**Figure 2.** A passive RFID tag (left) used in a retail store to protect against theft, and an active RFID tag (right) that is attached to the window of a car, used in New York State E-ZPass toll booths.

expected to generate power levels in the 2  $\mu$ W/cm² range [4]. Passive ambient harvesting requires no data processing, focusing solely on the reception and storage of ambient radio energy. Unfettered by the need for modulation or interpretive processing, ambient harvesting will have naturally improved efficiency across the range of input power, and can make use of more extreme design methodology in the later circuit stages.

As they are often solely responsible for sustaining power levels in isolated systems, ambient power harvesters cannot rely on periodic maintenance and may require extensive power buffering systems such as supercapacitors and microbatteries to sustain the circuit during periods of inactivity. This requirement is offset by a relatively stable source of power, since ambient RF power is usually supplied by a fixed source (or collection of sources) such as a transmission tower, power levels will not fluctuate over time to the same degree as commercial RFID handhelds. These circuits also benefit from an essentially infinite charging period, unlike communication-centric RFID applications that dictate a finite time period for circuit charging, and thus have more leeway in their selection of power buffering elements.

RF ambient harvesting is common for applications for which it is impractical or even impossible to change the node batteries, such as hazardous industrial maintenance or extreme environment monitoring. Since a node at the bottom of a hazardous gas can or a high altitude will be expected to function for long periods without maintenance, it is critical to design circuits that are reliable while still taking maximum possible advantage of available ambient power. Thus, ambient harvesters tend to have extended antennas and impedance networks but relatively few rectifier stages, and are followed by extensive buffering systems to preserve power for periods of high processing activity or low ambient exposure.

**Dedicated-Source RF Energy Harvesting:** A dedicated-source RF harvesting circuit at a short range is expected to generate power levels in the 50  $\mu$ W/cm<sup>2</sup> range [4]. An example is an RFID chip that is powered by an RFID interrogator [12].

In this paper, we focus on dedicated-source RF energy harvesting, which enables embedded devices not only to recharge batteries but also supports communication and wake-up functions, as will be described in the following section.

### **III. Motivating RF Applications**

Radio frequency power harvesting refers to the harvesting of the energy in a wireless signal through an antenna to power an embedded device. While the technology used to achieve this has certain universal similarities, the applications for wireless power harvesting are extremely diverse,

and may affect the design philosophy of the different elements within the circuit. Optimizations for one application may be detrimental to another, sacrificing range for efficiency, size for durability, or complexity for cost in ways suited only to a specific task. Thus, the needs of the application must be fully established before any design decisions take place, and be repeatedly reconsidered to make sure circuit tradeoffs are given proper weight in the final product. The following section provides three broad families of power harvesting applications to provide context for the surrounding research, along with brief technical descriptions of the design tradeoffs for each, which will be fully elaborated upon in later sections.

### A. Radio Frequency Identification (RFID)

RFID remains the most common and ubiquitous use of power harvesting technology. RFID has been widely accepted as the technological standard for supply chain management and industrial data tracking, and will undoubtedly see further expansion as the easily integrated transceiver chips (referred to as "tags") are adapted to smaller sizes and costs. For example, medical data acquisition is an emerging field that can significantly benefit from RFID [13]. Passive RFID design, which centers exclusively around wireless power harvesting, has a number of advantages over active design with traditional power sources [14], [15]. An example of each type of tag is shown in Fig. 2. Passive tags have extended lifetimes, do not require periodic maintenance, and can be fabricated at smaller size and cost than their battery powered counterparts. However, without the advantage of external power, passive tags must overcome a number of technical challenges to meet competitive range and performance requirements.

RFID is characterized by two way communication - the transceiver must not only receive data, but also transmit it via reflective backscatter managed by an internal oscillator and signal modulator. In addition, RFID chips must be extremely small and inexpensive to be commercially competitive, and are almost always implemented on a single integrated IC with an extremely small physical footprint. While these design parameters restrict the tools available to IC engineers, the massive scale on which RFID chips are produced invariably means that high precision technology is available; thus, parasitic effects can typically be predicted with higher precision than other technologies, and accounted for via simulation and optimized design models.

RFID functionality is highly limited, since their sub- $100\,\mu\text{W}$  power budget prohibits the implementation of elaborate on-chip computations (e.g., strong encryption [16]). RFID is most frequently used in supply chain tracking, personnel monitoring, and other commercial systems that typically require some onboard processing for every

query. This places a great deal of design emphasis on improving efficiency while reducing size and cost. Additionally, the need for two-way communication requires additional consideration for the modulation component, which sacrifices some power efficiency in order to communicate back to the source. Thus, RFID chips tend to have lower numbers of rectifier stages for efficiency, small and inefficient antennas, more complex impedance matching networks to provide backscatter, little to no power buffering to conserve space, and minimal computing power.

### B. Wireless Sensor Networks and Wake Up Radios

A relatively recent application for RF power harvesting is the enhancement and control of Wireless Sensor Networks, or WSNs [17]. These networks are defined as collections of autonomous systems to monitor environmental conditions, and may be used for research, industrial oversight, or biomedical applications. Unlike RFID, WSN nodes are responsible for more activity than the simple storage and transmission of data, and thus usually necessitate an onboard battery to power the relatively energy-intensive tasks of sensing and processing data (e.g., temperature, vibrational, or chemical monitoring). However, passive power harvesting systems may assist WSN nodes in a number of ways in conjunction with this primary power source [18]. Though their harvested power may not be sufficient to charge the larger scale energy storage, a passive chip may be used as a Wake Up Radio (WUR) that generates a wake up pulse upon receiving a command from a nearby transmitter [19]-[21]. Use of a fully passive WUR means that the active portion of the chip will only be active for short periods, and does not need to actively listen for commands during downtime. Designing the chip to be entirely power inert when not being queried for data can drastically improve chip lifetime, allowing systems that would otherwise require regular battery maintenance to expand to lifetimes of several years.

Wake Up Radios often do not require backwards communication, since their only purpose is to interpret a command and perform simple actions (e.g., waking up the main sensor system). Thus, they may take advantage of certain efficiency approaches that cannot be exploited by conventional RFID tags, by omitting efficiency-impeding elements such as modulators and digital processing, in favor of a simple correlator and pulse generator to wake the deactivated sensor system. This improvement in efficiency and lack of a backscatter system may lead to improvements in both range and operating time over default tags.

The specific applications for WSN networks thus tend to favor open environment monitoring, animal research, and isolated robotic systems. Thus, these designs tend to emphasize extreme range, but need very little power to perform their single wakeup operation and often have insignificant

27

Table 2. Commonly used Radio frequencies (RF) and corresponding wavelengths.  $\lambda/2\pi$  indicates the end of the inductive near field region.  $\lambda/4$  plays an important role in RFID antenna design.

| Frequency    | Band | Notes       | λ       | $\lambda/2\pi$ | λ/4    |

|--------------|------|-------------|---------|----------------|--------|

|              |      |             |         |                |        |

| 125-134 KHz  | LF   | unregulated | 2.3  km | 367 m          | 577 m  |

| 13.56 MHz    | HF   | ISM global  | 22 m    | 3.5 m          | 5.5 m  |

| 865-868 MHz  | UHF  | EU: ISM     | 35 cm   | 5.5 cm         | 8.7 cm |

| 902-928 MHz  | UHF  | USA: ISM    | 33 cm   | 5.2 cm         | 7.2 cm |

| 2.4-2.48 GHz | UHF  | ISM         | 12 cm   | 2 cm           | 3 cm   |

| 5.8 GHz      | SHF  | ISM         | 5.1 cm  | 0.8 cm         | 1.3 cm |

| 5.8 GHz      | SHF  | ISM         | 5.1 cm  | 0.8 cm         | 1.3 cm |

limitations on size and cost. WSNs tend to consist of large and efficient antenna/impedance matching networks, followed by many rectifier stages to improve sensitivity, and very few buffering and computing elements in the back end.

### IV. Background: Transmission Restrictions

Before approaching the individual sections of the RF power harvesting circuit in full detail, it is useful to define several operational metrics and legal limitations that will be continually referred to throughout this paper. In this section, the legal and logistical restrictions on frequency and power are defined and discussed.

### A. Transmission Range: r

The wavelength  $(\lambda)$  of an Electromagnetic (EM) wave radiated from an RF source at frequency f is

$$\lambda = \frac{c}{f} \Rightarrow \begin{cases} r \le \frac{\lambda}{2\pi} & \text{Near Field Inductive} \\ s \frac{\lambda}{2\pi} > r \le 2\lambda & \text{Near Field Radiative} \\ r > 2\lambda & \text{Far Field Radiative} \end{cases}$$

(2)

**Figure 3.** A  $P_{EIRP}$ =1 W, 915 MHz RFID reader/interrogator.

where c is the speed of light and r is the distance between the RF source (transmitter) and the RF receiver (e.g., RFID tag antenna). The significance of the  $\lambda/2\pi$  metric is that, this is the distance below which an RF transmitter and an RF receiver can establish an *inductive coupling*, similar to the coupling between the two ends of a transformer. Above  $\lambda/2\pi$ , communication is by means of *radiative coupling* [22].

While Eq. 2 ignores the size of the radiating antenna, these boundaries are typically placed at

$$\frac{\lambda}{10} < D < \frac{\lambda}{2} \begin{cases} r \le 0.62 \sqrt{\frac{D^3}{\lambda}} & \text{NF Inductive} \\ 0.62 \sqrt{\frac{D^3}{\lambda}} > r \le \frac{2D^2}{\lambda} & \text{NF Radiative} \end{cases}$$

(3)

$$r \gg \lambda, r \gg D \qquad \text{FF Radiative}$$

when the radiating antenna size, D, is taken into account [23], which can be simplified to Eq. 2 since optimum antenna sizes are proportional to  $\lambda$ . Up to  $r \leq 2\lambda$ , the communication between the RF source and the receiver is subject to strongly-interacting diffraction patterns, and is called *near field communication*.  $r > 2\lambda$  is the far field communication region which is strictly radiative and the propogating waves behave like plane waves. These two types of communications have a dramatic affect on the way RFID tags are designed: In the near field inductive region, the power decay is proportional to  $1/r^3$ , whereas, in the far field region, it is proportional to  $1/r^2$ . Table 2 shows commonly used RFID frequencies, their corresponding wavelengths  $(\lambda)$  and the end of their inductive near field distance  $(\lambda/2\pi)$ . The last column shows the  $\lambda/4$  value which will play an important role when designing RFID tag antennas as will be discussed in Section VII-F.

### B. RF Operational Frequency

RF power harvesting is possible at a large range of frequencies, from near-field inductive coupling at only a few KHz to satellite power transmission at  $\geq 30\,\mathrm{GHz}$ . However, the RFID standard and most significant breadth of research has centered around the UHF band (300 MHz–3 GHz range in Table 2). UHF band frequencies, which are also widely used by cellphones and mobile devices, are convenient for use in everyday spaces due to their balance between flexible range and low interference with environmental objects. However, the characteristics of the wave still vary significantly within the UHF range depending upon the wavelength parameter  $\lambda$ , which dictates antenna size, environmental attenuation, and

receiver component choice. Lower frequencies require larger antennas, attenuate less with environmental conductors, and require less precise circuit components for impedance matching; conversely, higher frequencies can utilize very small antennas, but attenuate heavily with range and are so sensitive to parasitics that they may only be feasible for Integrated Circuitry (IC). This tradeoff, along with its implications, is further discussed in Section VII.

The 125-134 KHz range shown in Table 2 found great use in wireless charging. The Qi standard [24], [25] introduced by the Wireless Power Consortium [26] is now implemented as an emerging means for wirelessly charging consumer devices such as laptops and cellphones, though, typically in the 110-205 KHz range [27]. 13.56 MHz, used in smart cards [15], [28], received great attention in early RFID research [14], [29]. These bands have a very large  $\lambda$  value and are best used for *inductive coupling* or magnetic resonance, rather than EM wave propagation or radiative coupling, which is dominant in the ISM frequencies. Inductive coupling can be an efficient method of power transfer at distances less than 1 m, but attenuates quickly at greater ranges, and additionally requires much larger antenna sizes and an altered circuit design to suit magnetic coupling. For these reasons, it cannot be used for far-field power harvesting, and is regarded as outside the scope of this paper.

In this paper, we focus on the most common 915 MHz and 2.4 GHz bands used in RFID and similar technologies, which are specified as open bands (called the *Industrial-Scientific-Medical* or *ISM bands*) within the United States and present opportunities for both directed and ambient power harvesting. 915 MHz is an easily accessible band with reasonable range and easily-fabricated reception circuitry, whereas 2.4 GHz may achieve greater ranges and smaller antenna sizes at the cost of more expensive impedance matching components and greater environmental attenuation. Other frequencies may theoretically be used, but may be limited by commercial ownership or strict regulation of legally transmittable power, and thus have less representation in academic literature.

### C. Antenna Transmission Power

For any wireless harvester device, energy must be gathered from the transmissions of one or more transceiver nodes that radiate RF power. The legal level of power output for these nodes, be they commercial transmission towers or simple consumer transmitters, is strictly regulated in most countries. The US limitation on maximum *Equivalent Isotropically Radiated Power* (EIRP) is 4 W, which applies to both the 915 MHz and 2.4 GHz bands of interest. EIRP is directivity independent, meaning that transmitted power cannot be increased with a narrower

beamwidth - thus, any gains in power reception may only be achieved through antenna gain or range restriction. Figure 3 shows an Impinj Speedway IPJ-R1000 RFID reader/interrogator, which has a  $P_{\rm EIRP}$ =1 W transmission power, operating at 915 MHz [12].

As several of the critical tradeoffs in a power harvesting system are range related, it is useful to estimate the power that will be available to a receiver node by distance. Several methods exist for predicting the power received by an antenna at a given range. The most commonly used equation is the *Friis Transmission equation*, developed by Harald T. Friis in 1945 to calculate the power transmitted between two antennas in theoretical free space as follows:

$$P_r = \frac{P_t G_t G_r \lambda^2}{(4\pi r)^2} \tag{4}$$

where  $P_t$  is the non isotropic transmission power,  $P_r$  is the incident power at the receiving antenna, and  $G_t$  and  $G_r$  are the gains of the transmitting and receiving antenna, respectively.  $\lambda^2/(4\pi r)^2$  is the free space loss factor.

This model can provide a useful upper limit for the maximum possible range available for a given transmitted power and antenna aperture. However, note that this equation assumes ideal free space, without any form of environmental attenuation - most real-world measurements will experience higher order distance attenuation,  $1/r^3$  or even  $1/r^4$ , causing far lower power levels in typical urban spaces. For predictions intended to account for these real world influences, a statistical log-shadow methodology may need to be used to determine a range of expected power values. Together, the EIRP and Friis Power define two important upper limits for every wireless harvester design, which can be used to determine early feasibility goals and estimates. Available power

at the antenna can never exceed the EIRP, regardless of range, and when evaluated at a distance will almost always fall below the Friis available power density, except for certain highly reflective environments. However, a few methods exist for attempting to boost instantaneous power while retaining the same average power, which are discussed further in Section IV-D.

### D. Transmission Improvements

For any RF signal to be received and harvested for power, it must first be sent by a transmitter. This may take the form of a single dedicated node, or as network of coordinated nodes, or even as ambient noise from a broadly modeled collection of sources. For RFID, single dedicated nodes, called RFID Readers, are the most common; alternatively, ambient power harvesters almost never have a single source and may receive from distant transmission towers and nearby mobile devices simultaneously. It is important to note that readers designed to actively interpret backscatter communication as well as transmit power tend to be quite sensitive and have vastly higher power and size traits than embedded tags, and thus have dramatically different design paths that do not adhere to any of the tradeoffs listed for receiver end technology. For this reason, hardware and networking protocols for transmitter systems are not included within the scope of this paper. However, the transmitted signal and its quality of reception may be improved through the use of specially optimized waveforms, careful antenna design, and improved decoding methods.

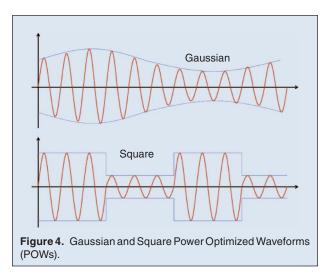

Power Optimized Waveforms (POWs): Carefully designed waveforms optimized to provide higher peak voltages can substantially increase the overall efficiency of the harvester system, and are implemented entirely on the transmitter end, requiring no changes to the receiver architecture. POWs utilize periodic amplitude fluctuation to maximize the voltage at the input of the RFID receiver, thereby increasing its efficiency [30]. Since the average RMS

30

power remains the same, POWs can be used to improve voltage-related performance without violating the power transmission limits present in most countries, and provide a means of overcoming rectifier voltage thresholds without the necessity of a system power increase. POWs can thus be used to increase both input sensitivity and efficiency of the receiver, with few tradeoffs in receiver architecture [31]. Several potential POW shapes exist, as outlined in [32]–[34], varying from Gaussian waveforms to simple square waves as shown in Fig. 21 that simply duty cycle the signal to achieve a higher voltage amplitude at the same RMS power. As will be described in Section VI, the *voltage* at the RF receiver input will play a crucial role in the efficiency of an RFID receiver.

The advantages of each waveform vary from application to application, and are often dictated by the data rate and desired bandwidth of the signal [34]. Due to their irregular signal, POWs may cause higher voltage rippling at the receiver, which must be smoothed with buffering systems before being passed to the IC. Additionally, in cases where backscattering communication is necessary, POWs may impose limitations on the types of modulation available and the error rate of these communications. A detailed description of modulation types will be provided in Section X-D. Circuits intended only for power harvesting do not suffer from these limitations. as they do not require demodulation or high bitrate protocols. Such systems may even use entirely chaotic waveforms to increase efficiency [35]. However, since many harvester-only systems are intended for ambient harvesting from commercial radio towers or other widedispersal sources, they do not have the luxury of a programmable transmitter and are thus unable to harness the advantages of POWs. Further potential applications of POWs are discussed in Section IX-C.

Signal Encoding: Passive harvesting systems depend upon the amplitude of the incoming signal for power, and thus many systems will benefit from the use of specialized encoding types such as Manchester encoding, where the DC value of the signal is independent of the data sent. Using these forms of encoding ensures a consistent average power entering the system, and ensures that data with a low overall duty cycle will not inadvertently starve the system of power. However, these more advanced encoding schemes may come at the expense of increased bandwidth and more complex demodulation circuitry. These tradeoffs should be carefully considered before deciding upon an encoding type that services both power supply and bandwidth/complexity constraints without debilitating the performance of either.

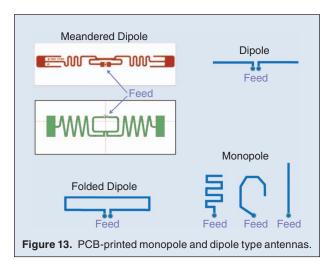

**Antenna Optimization:** The design of RFID antennas is a field of its own [36], [37], with a wide range of variables impacting the performance, size and cost of antenna

implementations [38]-[40]. Many antennas intended for commercial use are designed using evolutionary algorithms to reach optimal power transfer for a given size [41]. Others, especially those used for research applications, may be printed inexpensively with a PCB prototyping process, and dynamically modified when optimizing the performance of the circuit front-end [42]. The traits of these antennas are highly applicationspecific, and are dictated by preexisting requirements for cost, size, and manufacturing quality.

However, since all common antennas can be characterized by a set of ideal and non-ideal parameters, only a few aspects of antenna

design factor into the discussion of power harvesting efficiency. Most antennas are designed to minimize all reactive elements and assume a single real value for input impedance, usually  $50\Omega$ ,  $75\Omega$ , or  $300\Omega$  for commercial antennas, or a wide range of values for custom ones [43]. As larger resistance values result in higher harvested voltages as we will discuss in Section VIII, maximizing this value will lead to efficiency gains, though this may be difficult for electrically small antennas (ESAs) [44] or those with limited manufacturing detail [45]. It may also be assumed that at the high frequencies of UHF, some reactive components will exist as parasitics, and will have a non-ideal effect on the performance of the circuit. However these parasitics can be accounted for during the impedance matching process, and the voltage at the antenna may be improved through LC resonance boosting if certain conditions are met, a process that is further discussed in Section VII.

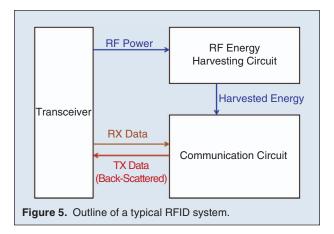

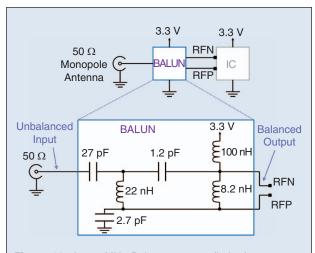

### V. Background: Building Blocks

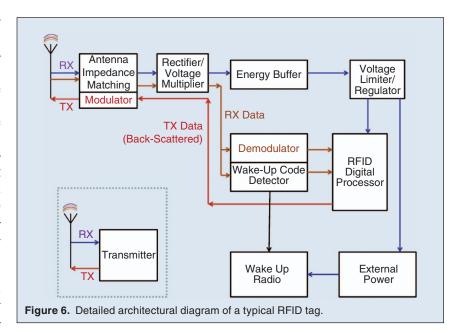

The general outline of an RFID system is shown in Fig. 5, consisting of a transceiver, harvester, and a communicator. The antenna assumes the *transceiver* role since it not only receives RF power and data, but also backscatters a portion of this power to be able to communicate back to the transmitter. *RF power harvester* is the portion of the circuit responsible for extracting the available power at the antenna efficiently and delivering it to the digital portion of the IC. *Communication* portion of the IC is responsible for demodulating incoming data and modulating outgoing data via backscattering, to establish a communication link with the source.

To accomplish these three tasks, RFID systems consist of several distinct circuit stages shown in Fig. 6. While

these stages can be individually characterized and have distinct roles within the circuit, each stage can dramatically impact the comparative performance of the others and the efficiency of the overall circuit. To successfully apply Figure of Merits (FoMs) to the design of an RFID system, it is critical to use consistent models and methodology, as an isolated approach may only improve a single metric and degrade others. To promote a global design approach and consistent treatment of the tradeoffs, the Analysis portion of this paper will be dedicated to illustrating each stage in detail and describing their effects on the system as a whole. The remainder of this section illustrates a roadmap of these stages.

**Transmitter:** While it is usually considered separately from the power harvester design, the efficiency of any power harvester system begins at the transmitter, which broadcasts the electromagnetic signal under the constraints of legal regulations and the physical transmission properties of the environment. While improvements in transmitter hardware and functionality will have no bearing on the power harvester efficiency, changes to the waveform of the transmitted wave may increase rectification efficiency by increasing the peak antenna voltage (consecutively, peak rectifier input voltage) as discussed in Section IV-D. The waveform of the transmitter may also be responsible for carrying information, both as instructions sent to the receiver, and as a carrier for backscattered communication being returned to the transmitter through impedance mismatch. These two communication signals may affect the efficiency of the power harvester through their duty cycle, as the power can fluctuate between high and low bits for certain forms of keying. However, this effect may be remedied through certain types of data encoding.

31

**Antenna Impedance Matching:** The first element of the power harvester itself is always the antenna, which creates a usable electronic waveform from the local RF power. An essential factor for any RF application is proper impedance matching to the antenna, since without a passive LC network, much of the power received at the antenna will be reflected back into free space. The specifics of this matching process vary based on the antenna size and construction, and also upon the passive methodology of the receiving circuit input. In many cases, changes in impedance reflection are also utilized by active circuit components to achieve the backscatter communication described earlier. The technological precision of this stage is often the most critical in the entire circuit, as even small changes in the resistive or reactive elements of the matching network impedance can cause disproportionately detrimental effects on the efficiency of the antenna reception. As an added complication, the matching network and incoming waveform may be utilized in some technologies to boost the signal's voltage amplitude using resonant amplification, raising the rectifier peak input voltage and thus the efficiency of the rectifier as well as the matching network.

Rectifier/Voltage Multiplier: Unfortunately, the voltages achievable via LC amplification alone are still typically insufficient to run a digital IC at the output of the power harvester system. Once the signal has been received by the antenna and amplified by the LC matching component, it must be passed through a voltage multiplier to reach a level usable by digital circuitry. Voltage multipliers often consist of several full wave rectifiers connected in cascade, which simultaneously rectify the sinusoidal AC waveform to DC and multiply it to a higher voltage. Due to the operating voltage drop over the diode or MOS components of the rectifier stages, the peak voltage at the input rectifier terminals is critical to the efficiency of the overall multiplier, and thus even small levels of voltage boosting in the LC stage can drastically improve the performance of this unit. Additionally, care must be taken that the number of cascaded multiplier stages is at the optimum point, as too few stages will result in an insufficient voltage output and sensitivity, while too many will generate harmful parasitic capacitance that will detrimentally affect the preceding antenna matching process.

**Energy Buffer, Voltage Regulator:** After the final stage of the multiplier, the DC output is typically passed into an *energy buffer* to remove ripple and provide consistent power availability. This buffer may be as small as a capacitor of several nanofarads, or as large as a digitally-controlled supercapacitor or rechargeable microbattery. The nature of the buffer element is dependent upon the application; many power harvesting applications do not

32

even consider the final capacitor to be a buffer, but simply another stage element of the multiplier topology. In other cases, a large and intelligently controlled power buffer is critical to the function of the circuit, and allows for substantial gains in range and operating time that could not otherwise have been attained. Performance of this stage is typically tied to the operation of the circuit's *voltage limiter* or *regulator*, and circuits with a sophisticated back-end may integrate these two systems together to improve power efficiency, decrease losses, and provide dynamic resistive matching to the antenna.

**RFID Digital Processor:** Finally, after being fully processed, the signal can be used to power the digital backend. This back-end is often the most heavily engineered element of the entire harvester, but is also the most application specific, and is difficult to generally categorize due to no specific digital element being present in every power harvesting circuit. The circuit can include any number of components, so long as they fall under the voltage and current consumption limits of the multiplier input and buffer element. Some ambient circuits may contain only as much circuitry as they need to manage the power buffer and regulator, utilizing a wake-able active component to perform processing operations as it becomes necessary. Other chips, such as RFID commercial trackers, may contain a detection-focused digital communications unit with oscillators, backscatter modulation, and nonvolatile memory. These elements may dynamically alter the structure of preceding units by altering the connections of the LC network, multiplier, and regulator to perform backscattering and reactive antenna calibration.

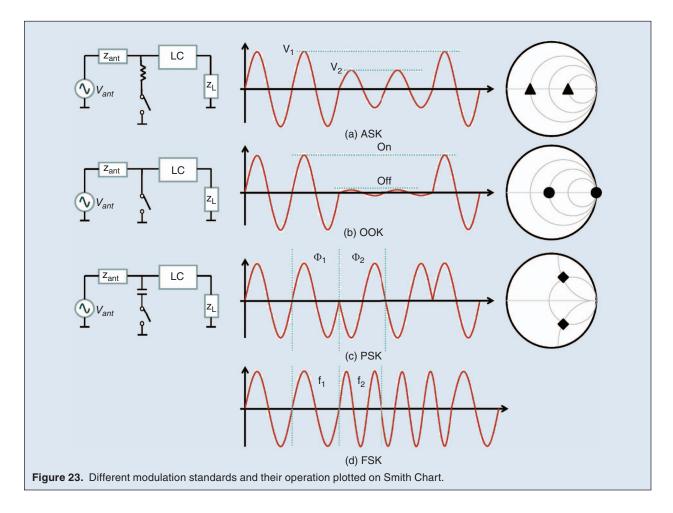

Modulator, Demodulator, Wake-Up Code Detector: The communication portion of a typical RFID circuit includes a demodulator that extracts the data being transmitted by the transmitter, as well as a backscattering modulator that modulates the load of the antenna to intentionally cause mismatches with the intention to transmit back data. A dedicated Wake-Up code detector can be incorporated into the RF circuit to detect an ID from the transmitted signal, which is used to wake up an active unit, such as a wireless sensor node.

Historically, the most common implementation of this series model of the wireless power harvester is a simple LC impedance matching front-end, a diode or transistor based Dickson-style multiplier, and a non-buffering limiter before the digital IC. These stages optimize power transfer from the antenna, boost the voltage to a suitable level for digital circuits, and prevent circuit damage from voltage overload, respectively. However, many publications have sought to improve upon this standard by altering one or more stages, by altering structure, changing process technology, or utilizing more specialized

mathematical models. To provide a full and accurate summary, each stage of the model presented above will be addressed independently across the following Analysis portion of this survey.

### VI. Background: Evaluation Metrics

As discussed in the introductory sections, the wide span of applications in which wireless power harvesting may be used means that no single Figure of Merit (FoM) may be used to evaluate the quality of a design. However, it is useful to define the efficiency, sensitivity, peak voltage and output voltage as the performance-critical evaluation metrics. These central FoMs determine the ability of the circuit to receive power at a distance and convert it efficiently, and while improving them may not always be the goal of a circuit designer, it is always critical that some standard of performance be met for the circuit to function competitively. Most of the critical tradeoffs in a power harvester circuit are between one of these metrics and the auxiliary metrics of low cost, low size, ease of manufacture, and high reliability. These main FoMs are defined as follows:

### A. Power Conversion Efficiency (PCE)

A widely used evaluation metric, Power Conversion Efficiency (PCE), refers to the proportion of the power received at the antenna that is successfully relayed through the harvester rectification circuitry and applied to the load. Here, we use the term load to refer to the parts of the circuit that need a steady DC voltage to operate, such as the communication circuitry, processing circuitry, sensing circuitry (if any) and more. With a slight abuse of terminology, we will use the term Integrated Circuit (IC) and load interchangeably, e.g., load current vs. IC current. A high PCE percentage indicates an efficient rectifier circuit, but power losses due to nonlinear component thresholds, leakage currents, and parasitics always exist in a practical circuit. PCE is defined [46]–[48] as the relationship between the absorbed power and the load power as shown in Eq. 5, and does not take signal reflection at the antenna into consideration.

$$PCE = \eta_c = \frac{P_{\text{load}}}{P_{\text{absorbed}}} = \frac{P_{\text{load}}}{P_{\text{incident}} - P_{\text{reflected}}}$$

(5)

### B. Sensitivity (P<sub>dBm</sub>)

The minimum power required for the IC of the receiving device to perform its intended task is defined as its Sensitivity. While less obvious than the blunt usefulness of PCE for evaluating circuit quality, sensitivity is often a more critical metric for evaluating the application of embedded systems, as minimum power is what dictates

the range, buffering requirements, and computing capacity of a device.

While maximizing sensitivity and efficiency are not mutually exclusive goals, their relationship may be complicated by the fact that PCE is often dependent upon input power. Operating at the absolute minimum possible input power usually results in a lowered PCE, since conversion efficiency tends to increase with input power and voltage amplitude. Additionally, designing circuits with technology such as zero threshold CMOS may increase sensitivity, but the leakage currents inherent to these processes may impair the circuit efficiency to unacceptable levels. A circuit seeking to competitively assert itself in the commercial market will have to balance between these two metrics, typically dictated by the application assigned to the IC and the ideal range at which the circuit should perform. Sensitivity is measured in DeciBel-milli-Watts (dBm) according to the formula below:

Sensitivity =

$$P_{dBm} = 10 \log_{10}(P_{mW})$$

(6)

where  $P_{dBm}$  and  $P_{mW}$  are the power values expressed in terms of Decibel-milliWatts and milliWatts, respectively. As an example, most competitive far-field RFID circuits have a sensitivity between -25 dBm and -10 dBm, corresponding to operating input power levels between  $3\,\mu\rm W$  and  $100\,\mu\rm W$ .

### C. Peak Passive Voltage (V<sub>peak</sub>)

The efficiency and sensitivity of a standard power harvester circuit are highly proportional to the amplitude of the sinusoid between the LC matching network and the rectifying stage ladder. This relationship, unique to wireless power harvesting, is commonly referenced in the literature but never given a specific emphasis. For the purposes of simplicity, this paper will define the *Peak Passive Voltage* ( $V_{\rm peak}$ ) as the peak amplitude of the voltage sinusoid observed at the output of the antenna impedance matching network (i.e., input terminals of the rectifier/voltage multiplier).

$V_{\rm peak}$  defines the sensitivity and efficiency of the rectifier via its relationship to the voltage threshold  $V_{\rm TH}$  at the rectifier input terminal. As the  $V_{\rm peak}$  rises above  $V_{\rm TH}$ , the PCE will increase, but allowing the  $V_{\rm peak}$  to drop below  $V_{\rm TH}$  will deactivate the multiplier, defining the sensitivity.  $V_{\rm peak}$  is also related to the rectifier output voltage, as the rectifier ladder will output a voltage multiple of the  $V_{\rm peak}$  depending upon the number of stages.

### **D. Rectifier Output Voltage** (Vout)

The DC voltage amplitude at the output stage of the rectifier/voltage multiplier is defined as the Output Voltage and is usually recorded at the absolute worst case scenario (i.e., minimum input power conditions). In general, output voltage is seen as a technological requirement rather than a metric to optimize, since the operating voltage of most IC technologies cannot be further improved without significant power losses or increases in cost, and thus this performance measure can only dictate the number of stages in the voltage multiplier.

### E. Regulator Dropout Voltage (V<sub>dropout</sub>)

The responsibility of the voltage limiter/regulator is to reduce  $V_{\rm out}$  down to  $V_{\rm DD}$  and regulate it at this stable DC value. Since the regulator will require a voltage difference between its input and output (referred to as "dropout",  $V_{\rm dropout}$  in the literature),  $V_{\rm out} > V_{\rm DD}$  must hold for good regulation. The regulation is achieved according to

Regulator Dropout Voltage =

$$V_{\text{dropout}} = V_{\text{out}} - V_{\text{DD}}$$

(7)

### F. Load Voltage (VDD) and Load Current (IDD)

The entire digital portion of the RF circuit is typically fed from a stable DC voltage,  $V_{\rm DD}$ . The current draw from  $V_{\rm DD}$  by the digital back-end (the load) is referred to as  $I_{\rm DD}$ . As most IC technologies require voltages of over  $V_{\rm DD} > 1\,\rm V$  to function properly,  $V_{\rm DD}$  is often the dominating parameter for sensitivity, since it is assumed that any lower values of input power will result in an insufficient voltage to power the digital section of the IC. Voltage values above acceptable levels are managed by a limiter or a regulator, preventing damage to sensitive IC components.

### G. Overall System Efficiency $(\eta_0)$

34

For cases where the entire circuit needs to be collectively examined for efficiency, rather than just comparing rectifier performance, the overall efficiency,  $\eta_o$ , can be examined using Eq. 8 based on the incident power [46], and thus overall power efficiency will include efficiency losses from impedance mismatch and reflective scattering at the antenna level.

Overall System PCE =

$$\eta_o = \frac{P_{\text{load}}}{P_{\text{incident}}}$$

(8)

Since  $\eta_o$  is heavily dependent on the antenna and circuit process precision for the passive components, it may vary significantly between different implementations of the same circuit design, and is less commonly included in RFID literature as a performance metric. Implementations of LC matching circuits are often intentionally excluded through the use of a hard-wired RF signal generator for testing, or are mathematically described as having abstracted efficiency boosting traits, leaving any numerical record of efficiency to the manufacturer once the full benefits of manufacturing scale have been

applied. For the purpose of comparing publications within this survey, studies that have examined the overall efficiency rather than the conversion efficiency will be clearly indicated to prevent confusion.

Eq. 8 incorporates efficiency losses due to the three distinct stages that the incident antenna power must transfer through to turn into a stable load power @  $V_{\rm DD} \times I_{\rm DD}$ . The antenna and the impedance matching network efficiency is the ratio of the incident antenna power and the power delivered into the rectifier input as follows:

Antenna/LC Nwk Efficiency =

$$\eta_{\text{ant}} = \frac{V_{\text{rect}} \times I_{\text{rect}}}{P_{\text{Incident}}}$$

(9)

where  $V_{\rm rect}$  and  $I_{\rm rect}$  are the RMS voltage and current at the input of the rectifier. Note that,  $\eta_{\rm ant}$  includes the power loss due to the need to communicate via back-scattering. The rectifier efficiency is the ratio of the incoming rectifier power and the DC power output from the rectifier into the regulator and can be defined as:

Rectifier Efficiency =

$$\eta_{\text{rect}} \approx \frac{V_{\text{out}} \times I_{\text{DD}}}{V_{\text{rect}} \times I_{\text{rect}}}$$

(10)

where  $I_{\rm DD}$  is the load current, which is approximately equal at both the input and the output of the regulator, and  $V_{\rm out}$  is the output voltage of the rectifier. The regulator efficiency is dominated by the required minimum dropout voltage and is defined as  $\eta_{\rm reg}$  as follows

Regulator Efficiency =

$$\eta_{\text{reg}} \approx 1 - \frac{V_{\text{dropout}}}{V_{\text{out}}}$$

(11)

which is typically less than Eq. 7 due to the quiescent current sources required to operate the regulator, hence our  $\approx$  notation. Combining Eq. 9, Eq. 10, and Eq. 11, we arrive at Eq. 8, which can be rewritten as

$$\eta_o = \frac{P_{\text{load}}}{P_{\text{incident}}} = \eta_{\text{ant}} \times \eta_{\text{rect}} \times \eta_{\text{reg}}$$

(12)

where  $\eta_{\rm ant}$ ,  $\eta_{\rm rect}$ , and  $\eta_{\rm reg}$  are the individual efficiency of the antenna and the LC matching network including reflective power losses at the antenna, the rectifier ladder, and the voltage limiter/regulator, respectively.

### H. Auxiliary Metrics

Other metrics also affect the circuit design philosophy. *Cost per unit* is defined as the monetary expense of manufacturing an individual design, a critical value for circuits in commercial products and other high volume applications. Cost is generally related to *ease of manufacture*, which will degrade with unusual technologies - much of the literature in the 2000–2010 era has focused on converting from the efficient but difficult to manufacture Schottky diodes to the more universal CMOS technology. *Physical size* may also be an important merit for commercial and

research applications, which can exclude large antennas or high-area LC matching networks from use in the design. *Reliability* may be a concern for ICs with an unusually long expected lifetime or stressful environment, which may necessitate larger circuits, PCE-lowering compensation overhead, and redundant circuit elements.

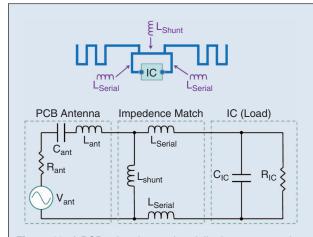

# RX Transmitter Antenna Impedance Matching Figure 7. Antenna Impedance matching stage.

# VII. Analysis: Antenna Impedance Matching

A common factor in any power harvester unit, whether the end application is RFID, ambient harvesting, wakeup or detection, is the use of an impedance matching network and a voltage multiplier. It is critical that these two circuit elements are approached through co-design, as the construction of each has a dramatic effect on the performance of their counterpart, and failure to properly model their relationship may result in substantial efficiency reduction through power reflection and stage threshold losses. To tune the circuit to application specifications, many publications examine the two elements independently before using an iterative optimization algorithm in simulation, revising circuit values until the best values are obtained [49]. Following this design pattern, this paper will approach the research on impedance matching and rectifier design as independent sections, which should be repeatedly examined throughout the design process to prevent inadvertent undermining of prior performance gains.

### A. The Impedance Matching Network

Figure 7 shows the placement of the impedance matching stage. As the element directly responsible for antenna management and waveform tuning, the mathematics of the impedance matching network revolve around two figures of merit, the *reflection coefficient* and the *passive network voltage gain*. The reflection coefficient ensures that the circuit does not radiate power back into free space at the antenna aperture by precisely matching the real and imaginary impedances of the circuit, while the passive voltage gain provides a slightly higher  $V_{\rm peak}$  at the rectifier to overshoot the threshold voltage  $V_{\rm TH}$  and increase efficiency. These metrics are determined by the antenna *Characteristic Impedance*, the *Input Impedance* of the rectifier, and the *Quality Factor* of the matching network.

Impedance matching at the antenna refers to designing of a network of passive components that transform two mismatched impedances to equivalent ones. The matching of the antenna to the rectifier requires such a network to minimize the *reflection coefficient*, shown in

(Eq. 13), which assists in modeling the amount of energy that will be reflected:

Reflection Coefficient =

$$\Gamma = \frac{Z_{\text{rect}} - Z_{\text{ant}}^*}{Z_{\text{rect}} + Z_{\text{ant}}^*}$$

(13)

where  $Z_{\rm ant}=R_{\rm ant}+X_{\rm ant}$  is the antenna impedance,  $Z_{\rm ant}^*$  is its complex conjugate, and  $Z_{\rm rect}=R_{\rm rect}+X_{\rm rect}$  is the input impedance of the rectifier stage. Thus, it can be seen that maximum power transfer (minimum power reflection) will occur when the resistive elements ( $R_{\rm ant}$  and  $R_{\rm rect}$ ) are equal, and the reactive components ( $X_{\rm ant}$  and  $X_{\rm rect}$ ) are of opposite sign [50]. Failure to achieve this case will result in some fraction of the total power being reflected away from the rectifier, quantified as the *Power Reflection Coefficient*  $|\Gamma|^2$

Power Reflection Coeff. =

$$|\Gamma|^2 = \left|\frac{Z_{\text{rect}} - Z_{\text{ant}}^*}{Z_{\text{rect}} + Z_{\text{ant}}^*}\right|^2$$

(14)

Reflection of incident power at the antenna (i.e.,  $|\Gamma|^2 < 1$ ) reduces the available power to the rectifier, thereby decreasing the overall efficiency as shown below

$$P_{\text{avail}} = P_{\text{incident}} - P_{\text{reflected}} \tag{15}$$

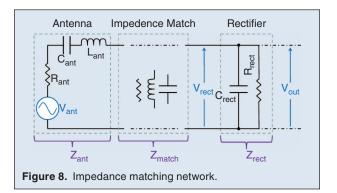

As shown in Fig. 8, even well designed antennas that are designed to appear as the pure resistive industry standards  $R_{\rm ant} = 50\Omega$  or  $75\Omega$  may contain traces of inductive  $L_{\rm ant}$  or capacitive  $C_{\rm ant}$  parasitic impedance.

# Circuits seeking to maximize antenna absorption and voltage gain must carefully consider the tradeoffs created by the components in their matching network and the resonant traits of their arrangement.

The input impedance of the rectifier  $(Z_{\rm rect})$  includes a relatively large resistor  $(R_{\rm rect})$  at low power levels, and a small capacitive load  $(C_{\rm rect})$  due to the parasitic capacitances of the rectifying elements. The impedance matching network has an impedance of its own  $(Z_{\rm match})$ , and is required to cancel the reactive units and deliver the power from the antenna resistance  $R_{\rm ant}$  (also referred to as *radiation resistance*) to the load resistance  $R_{\rm rect}$ . Several different methods of impedance matching are described in this section, which all attempt to implement  $Z_{\rm match}$  using various topologies of LC components.

### B. Passive LC Voltage Boosting

The primary responsibility of the LC matching network is to transfer the maximum amount of power from the antenna radiation resistance ( $R_{\rm ant}$ ) to the resistive portion of the rectifier ( $R_{\rm rect}$ ). LC matching network design must take into account the rectifier parasitic capacitance ( $C_{\rm rect}$ ) resulting from the input capacitance of the active devices used in the rectifier, such as Schottky diodes and MOS transistors. An observation of Fig. 8 reveals that, as long as  $R_{\rm rect} > R_{\rm ant}$ , a voltage boost at  $R_{\rm rect}$  can be achieved in relationship to  $V_{\rm ant}$ . The antenna incident power is ( $V_{\rm ant}^2/R_{\rm ant}$ ). Once the matching network cancels out the reactive portion of the impedance between  $R_{\rm ant}$  and  $R_{\rm rect}$ , this power is shared between the  $R_{\rm rect}$  and  $R_{\rm ant}$ . Maximum attainable LC voltage boost (named "passive" voltage boost) is therefore [51]

Passive Voltage Boost =

$$A_{LC} = \frac{V_{\text{rect}}}{V_{\text{ant}}} \le \frac{1}{2} \sqrt{\frac{R_{\text{rect}}}{R_{\text{ant}}}}$$

(16)

### C. Quality Factor (Q Factor) Analysis

36

Due to the threshold voltage drops and the power loss due to those drops, the effective input resistance of the rectifier is typically much lower than the calculated value under "ideal" assumptions, typically more than an order-of-magnitude or worse. Furthermore, the LC boosting circuitry consists of inductors that are constructed from metal wires inside an IC which contain resistive and capacitive parasitics. While the losses due to the capacitive portion of the parasitics can be eliminated by creating their complex conjugates during the impedance matching process, resistive parasitics simply create unpreventable power losses. This necessitates the definition of a *Quality Factor* metric, *Q*, that quantifies the

potential for a component to efficiently store and deliver energy. For example, an inductor with inductance of L(i.e., a reactance of  $X = \omega L$ ) and a series resistive parasitic R will have a Q as follows

Inductor Quality Factor =

$$Q_L = \frac{X}{R} = \frac{\omega L}{R}$$

(17)

where  $\omega$  is the frequency at which the inductor is working, in radians per second. Following the definition in Eq. 17, an ideal inductor with no resistive parasitics will store and deliver energy at 100% efficiency, i.e.,  $Q_L = \infty$ . This is practically not possible, as every wire that the inductor is made out of will have some resistance. In an IC design,  $6 < Q_L < 40$  are typical [14], [52], and  $Q_L = 40$  is very good.

Q can be generalized to RLC networks as follows

Quality Factor =

$$Q = 2\pi f \times \frac{\text{Energy Capacity}}{\text{Power Loss}}$$

(18)

where f is the operation frequency of the RLC network, Energy Capacity is the total amount of energy the network can store, and Power Loss is the continuous power loss endured by the resistive elements in the network. High Q values for the antenna impedance matching circuit improve the performance by boosting the voltage at the input at the rectifier, raising the  $V_{\text{peak}}$  and thus simultaneously improving the efficiency, sensitivity, and output voltage of the entire system. Circuits with a higher Q will oscillate with a greater amplitude, leading to a larger voltage gain at the output. Several studies have used this property to compensate for smaller antennas with a low radiation resistance, which causes a lower innate voltage amplitude at the antenna terminals. However, this improvement comes with some costs, specifically the non-trivial difficulty of evaluating Q values in complex matching networks, and the high component quality required to meet the stringent values required in these equations.

Q can be determined from the resistive and reactive elements of the matching network, but the exact formula will vary between configurations, and thus a matching circuit will have a Q value that is highly dependent on its topology. These equations can be extremely complex, and difficult to produce, even in simulation. Thus, a tradeoff between managable complexity and  $V_{\rm peak}$  can occur in the design of this component. Q is also limited by the individual quality factors of the passive network components, which will have their own Q values, damping their

oscillation. Note that the low-power embedded technology used in RFID often severely limits component Q values, especially for inductors, leading many papers to disregard Q related bandwidth reduction as a negligible concern as no process can reach Q value where it would become relevant to the 902-928 MHz range. It is possible that this conclusion may change as circuit manufacturing for RF harvesting becomes more advanced, and extremely high Q components such as quartz L resonators become available for use in design [53], [54]. However, these limitations still present significant obstacles for designers hoping to leverage the Q boosting opportunities of LC circuits. By carefully designing the matching circuit, a voltage boost at the IC input can be achieved due to the high resistance of the load. The authors in [52] report a simulated voltage boost of 3 to 8 based on different parasitic values.

### D. Impedance Matching Network Topologies

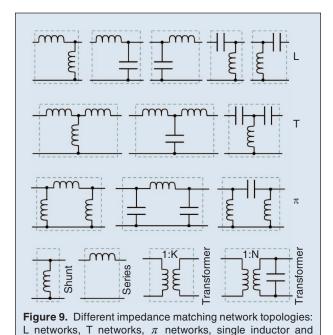

Figure 9 depicts most commonly used impedance matching networks, although many other configurations are possible by replacing certain capacitors with inductors, and vice versa. Additionally, more stages than what is shown in Fig. 9 can be utilized if a large bandwidth needs to be achieved by the LC network. All of these circuits, and many other alternatives of them exist to simply implement the  $Z_{\rm match}$  described in Fig. 8. Although implementing  $Z_{\rm match}$  is a straightforward task by using a Smith Chart as will be explained shortly in this section, different topologies have a dramatically different effect in the way parasitics are handled by the LC network. These topologies will be explained individually:

L Networks: The L network is named due to the way L and C components are connected in an L shape. This setup thus matches the antenna to the rectifier, and may also cancel out stray reactive impedance. At the selected circuit frequency, this equivalent circuit will appear as a resonant LC tank, with a resistive load matched 1:1 with the input resistance to maximize power transfer.

$\pi$  and T Networks: Many alternatives to the L network exist, which utilize different arrangements of passive components to perform the same mathematical transformation of apparent impedance. These alternatives are  $\pi$  networks, T networks, or even more complex arrangements with many stages of capacitors and inductors. These networks do not alter the final impedance match, but instead alter the Quality Factor of the network, thereby potentially improving the passive voltage boost,  $A_{\rm LC}$ .

**Inductor-Only Networks:** In response to tradeoffs and limitations in designing L networks, studies such as Barnett et al. [47] have questioned the use of LC passive voltage boosting. Under certain conditions where the apparent load resistance has been reduced and the radiation resistance of the antenna is high, the ratios used in

the evaluation of Q will be low, and the matching network will not provide much additional passive voltage boosting regardless of the network topology. Additionally, when integrated into standard CMOS processes, many microscale passive components have a low Q, defined as their intrinsic reactance over resistance. Thus, the advantages of passive voltage boosting may be lost, or worse, the Q factor will actually attenuate voltage gain. Barnett et al. [47] have suggested that a standard L network be replaced by a simple Shunt or Series inductor or a 1:K transformer, as shown at the bottom of Fig. 9. These designs will provide no voltage boosting, but can be cheaper to manufacture and test, and will be more efficient when paired with high-power loads that appear as a small resistance at the entrance of the rectifier.

**Transformer-based Networks:** A study by Soltani et al. [51] has investigated the use of a CMOS-process integrated 1:N transformer and a capacitor as an impedance matching network, shown on the bottom right of Fig. 9. Transformers make use of a pair of coupled inductors that perform voltage magnification and resistive transformation relative to their coil ratio via induction. Note the difference between Soltani et al. [51] who uses an additional capacitor, effectively making it an LC network vs. Barnett et al. [47] who only use a transformer. Thus, Soltani et al. can provide both voltage step up and resistive matching simultaneously, augmented by reactive components at each end to form dual LC tanks and cancel unwanted reactances. While transformers have long been used for impedance matching in radio applications, they are not usually seen as practical at the frequencies required for RFID due to implementation

Transformer-based networks.

37

cost and core losses. However, when integrated on chip or in limited-issue applications where cost is not an issue, transformer use may lead to efficiency gains and holds potential for future research.

As matching network performance is dependent upon a number of factors, including component quality, chip process, cost, size, and frequency, no superior option can be recommended for any given application. Circuits seeking to maximize antenna absorption and voltage gain must carefully consider the tradeoffs created by the components in their matching network and the resonant traits of their arrangement. Once a design philosophy appropriate for a specific application has been decided upon, a complementary rectifier can be chosen and co-optimization of these two units can begin. This rectifier element has the most research history of any section of the wireless power harvester, and is discussed at length in Section VIII.

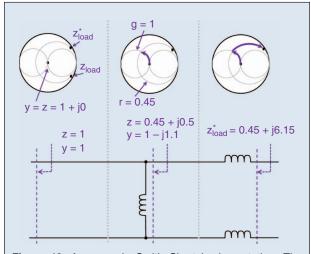

### E. Smith Chart-Based Matching Network Design

A Smith Chart is possibly one of the most practical and intuitive design tools to implement impedance matching networks and can be applied to any one of the topologies

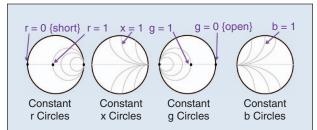

**Figure 10.** An impedance Smith Chart with four different types of circles to convert between normalized impedance (z = r + jx) and normalized admittance (y = g + jb) throughout the impedance matching process.

**Figure 11.** A PCB-printed meandered dipole antenna and an impedance matching circuitry built using three impedances that are a part of the PCB pattern [28].

shown in Fig. 9. An example Impedance Smith Chart is shown in Fig. 10, which contains four different types of circles that traverse a constant resistance (r), constant reactance (x), constant conductance (g), or constant susceptance (b). Every point on the Smith Chart denotes an impedance value z=r+jx, and a corresponding admittance value y=g+jb. Note our lower case notation, which implies normalized impedance and admittance values, by computing  $z=Z/Z_{\rm ant}$ , or more generally the characteristic impedance of the source  $(e.g., 50\,\Omega)$ . This normalization allows us to use the Smith Chart independent of the frequency.

Inductors add to the reactance and do not change the resistance (ignoring the parasitic resistance). Therefore, adding a series inductor to a circuit is equivalent to moving the current impedance "up" a constant resistance circle, during which, we move from  $z = r + jx_1$  to  $z = r + jx_2$ . The contribution of the inductor to the x value is  $x_2 - x_1$ , thereby allowing us to calculate its inductance. Seriesconnected capacitors perform an identical transformation, except, they add negative reactance, thereby traversing a constant-resistance circle in the "down" direction. Shunt-connected inductors and capacitors are identical, except, they add to the admittance, rather than impedance. Therefore, to compute the contribution of a shunt-connected element, it would make the most sense to switch to the admittance and use the constant g curves. Using these curves, inductors still move us up, and capacitors move us down. The goal of the design of an impedance matching network is to determine a list of shunt/series capacitor/inductor elements to start at the source impedance and end up at the load impedance.

**Algorithm 1** Methodology in using an impedance/admittance Smith Chart (shown in Fig. 10) to design an impedance matching network.

- 1. Normalize the source impedance  $Z_{\text{ant}}$  to get  $z_{\text{ant}}$

- 2. Normalize the load impedance  $Z_{load}^*$  to get  $z_{load}^*$

- 3. Plot  $z_{\text{ant}}$ ,  $z_{\text{load}}^*$  on the Smith Chart

- 4. The goal is to go from  $z_{ant}$  to  $z_{load}^*$

- 5. During traversals, use one of the four types of circles

- 6. Series elements: use constant r, constant x circles

- 7. Shunt elements: use constant g, constant b circles

- 8. Inductors move us up. Capacitors move us down.

- 9. At any point, to convert from z to y = 1/z, use the corresponding  $\{r, x\}$  vs.  $\{g, b\}$  intersection

- 10. Keep traversing circles until you reach  $z_{load}$ .

- 11. The elments you used is the matching network

Algorithm 1 shows the impedance matching methodology using a Smith Chart. An example will clarify this methodology: Dobkin [28] shows a PCB-printed meandered dipole antenna construction with a total antenna width of 9 cm using the configuration in Fig. 11.

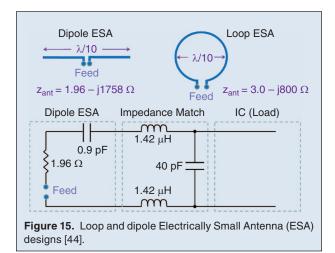

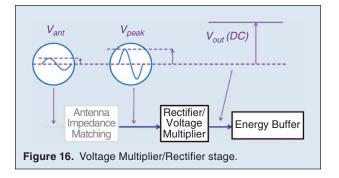

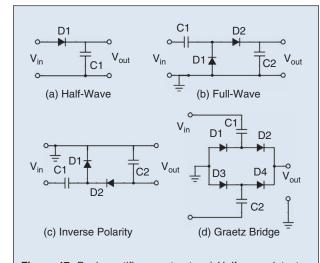

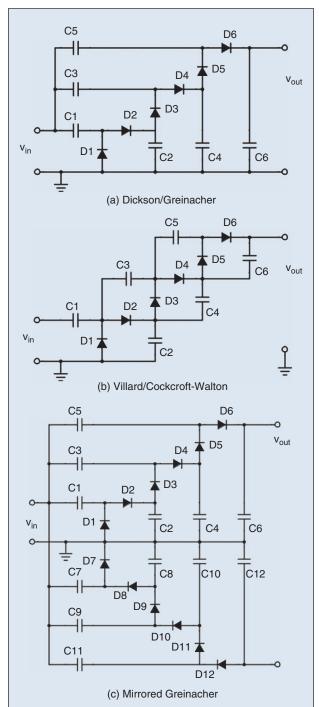

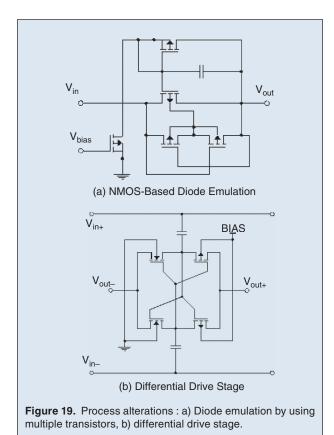

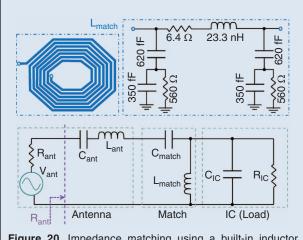

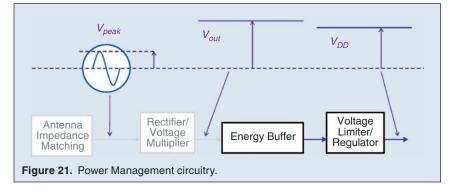

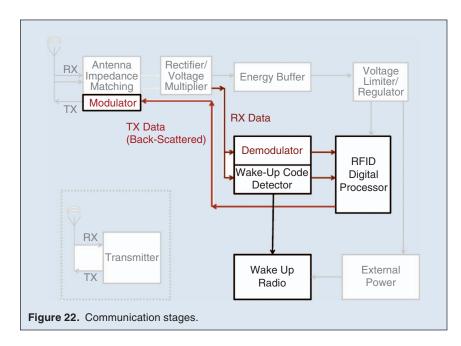

Radiation resistance of the antenna is  $R_{\rm ant}=25~\Omega$ . Operating frequency is 860–960 MHz. Antenna parasitics are  $C_{\rm ant}=0.45~\rm pF$ ,  $L_{\rm ant}=63.5~\rm nH$ , which cancel each other out at 940 MHz. Therefore, we will assume a pure resistive antenna resistance of  $Z_{\rm ant}=25~\Omega$ . The IC load (i.e., input of the rectifier) is  $R_{\rm IC}=2200~\Omega$ ,  $C_{\rm IC}=1.1~\rm pF$ . This requires PCB-printed matching inductors  $L_{\rm serial}=11~\rm nH$  and  $L_{\rm shunt}=4~\rm nH$ .