#### INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

# **Incorporating Circuit Level Information into the Retiming Process**

by Tolga Soyata

Submitted in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Supervised by Professor Eby G. Friedman

Department of Electrical and Computer Engineering

The College

School of Engineering and Applied Sciences

University of Rochester Rochester, New York

1999

UMI Number: 9961367

Copyright 2000 by Soyata, Tolga

All rights reserved.

#### UMI Microform 9961367

Copyright 2000 by Bell & Howell Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

Bell & Howell Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

# **Dedication**

This dissertation is dedicated to my country Turkey, where my soul belongs to.

Currently, the sum of the market capitalizations of all Turkish companies in the Istanbul bourse is less than Intel's market cap. My goal is to see many Intel's in the Istanbul bourse before my last breath.

## **Curriculum Vitae**

The author was born in Istanbul, Turkey on January 23, 1967. He attended Istanbul Technical University from 1984 to 1988 and graduated with a Bachelor of Science degree in Electrical Engineering. He received his Master of Science degree in Electrical and Computer Engineering from Johns Hopkins University, Baltimore, Maryland in 1992. He began further graduate studies in the Electrical and Computer Engineering field at the University of Rochester in 1992. His research interests include sequential circuit optimization by using pipelining, retiming, and clock scheduling techniques. He implemented a retiming algorithm that incorporates low-level circuit issues such as clock delays, variable register delays, and interconnect delays into the retiming process. He has published four conference papers and one journal paper. He pursued his research in the field of high performance VLSI design under the direction of Professor Eby G. Friedman.

## Acknowledgements

I thank the Turkish government for sponsoring me throughout my Master's studies at Johns Hopkins University. I also thank the University of Rochester for sponsoring me during the early phase of my Ph.D. degree.

I am very thankful to the government of the United States for providing the infrastructure for my business. Without such an infrastructure, I would not be able to start my business and/or make such progress. Although I am a successful entrepreneur, I am very well aware that I would not be able to efficiently start and grow a business if the infrastructure was not there. It is clear to me that Soyata Computers is not only the success story of Tolga Soyata, but also just another success story of the United States.

Between 1981 and 1984, I was at Ankara Fen Lisesi (Ankara Scientific High School)

— AFL. I owe a very strong math and science background to AFL and my teachers at AFL. The foundation I built up at AFL will be with me for the rest of my life. I cannot thank my teachers at AFL enough.

Between 1984 and 1988, I built up a very strong background at Istanbul Tech University (ITU). I cannot thank my professors enough since I owe the strong fundamental knowledge base in Electrical and Computer Engineering to them. I thank my advisor Prof. Hakan Kuntman, who always encouraged me. Prof. Ahmet Dervisoglu and Prof. Ahmet Kayran have always been great role models for me. I thank the Computer Science Department, especially Prof. Esref Adali, for encouraging me to get involved in

Computer Science.

Between 1990 and 1992, I further strengthened my Electrical and Computer Engineering background at the Johns Hopkins University (JHU). JHU is where I developed a strong practical knowledge base. Prof. Andrew Goldfinger taught me how to apply theoretical DSP knowledge to real life. Prof. Andreas Andreou interested his entire class in silicon retinas and analog VLSI. Professors at the Computer Science Department helped me build an invaluable computer science background.

The seven years I spent at the University of Rochester taught me both research and business. The company I started seven years ago became a success story in Rochester. I thank all of my employees for making it possible for me to continue to study for my Ph.D. while I was running the company. I also thank my lab mates, Brian Cherkauer, Victor Adler, and Ivan Kourtev, for sharing their valuable views with me.

I thank Prof. Kevin Parker for always believing in my business and supporting me. I also thank him for recommending me to the e-commerce committee and to the scientific editor of the UR newspaper, Tom Trickey. I thought I would fail my Ph.D. many times due to my decision of starting a business. I might not be leaving the University of Rochester with an exceptional Ph.D. that Prof. Friedman initially expected from me, however, it is an honor to see that both Prof. Friedman and Prof. Kevin Parker support my decision of choosing the business world over the academic world.

I thank Professor Eby G. Friedman for being a father, a friend, and a mentor for me.

I also thank him for being very patient with me. The lessons he taught me will help me for the rest of my life. I already started using his soft-but-hard approach towards my own employees. Although I disagreed with Prof. Friedman at times, I am amazed with the same response I am getting from my employees. I will always use his bottom-line oriented approach and zero tolerance for mistakes during my career. Prof. Friedman went far beyond teaching me academics, but changed my life once and forever.

#### **Abstract**

The advances in CMOS technology over the past decades have created the need for the design of extremely complex Very Large Scale Integration (VLSI) Integrated Circuits (IC)s. The simultaneous progress in Computer-Aided Design (CAD) tools enable large design teams to work independently on sophisticated VLSI projects. The pipelining process is widely utilized in VLSI ICs as a performance enhancement tool. Efficient automated pipelining algorithms have been developed to permit the application of pipelining to large integrated circuits. The emerging technique of retiming, on the other hand, has not found its way into the VLSI circuit design process due to complex and non-practical algorithms. Therefore, algorithms and/or methodologies to help achieve retiming with simpler and practical algorithms can significantly improve the acceptance of retiming techniques in standard VLSI design methodologies.

A retiming methodology is presented in this dissertation to model low-level circuit characteristics in VLSI ICs. This objective is achieved by modeling low level circuit parameters using the Register Electrical Characteristic (REC) model. The path delays in a VLSI IC are defined from register-to-register based on this REC model. The REC model forms the core of the retiming algorithms introduced in this dissertation. The REC model, for the first time, permits incorporating low-level circuit issues into the retiming process, thereby yielding significantly more accurate retiming results than the existing retiming algorithms currently described in the literature. Path monotonicity constraints

have been developed to permit the application of standard Linear Programming (LP) based techniques to the general retiming process. These monotonicity constraints permit circuits to be retimed with low-level characteristics with significantly less CPU time complexity.

Although the application of retiming to practical circuits has not as yet become common place, the research described in this dissertation is a significant improvement in making retiming into a practical and useful design methodology. The relationship between clock scheduling and retiming is also discussed in this dissertation where it is shown that the two processes are inextricably intertwined. The results of applying retiming to benchmark circuits have demonstrated performance improvements of up to 50%. When clock scheduling techniques are combined with retiming techniques while including low-level circuit characteristics, retiming can significantly improve the design efficiency and performance of the next generation VLSI circuits.

# **Table of Contents**

| Chapter I | Intro                  | duction |                                                                        |  |  |

|-----------|------------------------|---------|------------------------------------------------------------------------|--|--|

| Chapter 2 | Theoretical Background |         |                                                                        |  |  |

|           | 2.1                    | Terms   | Related to Synchronous Circuits                                        |  |  |

|           | 2.2                    | Repre   | Representing Synchronous Circuits Using Graphs                         |  |  |

|           |                        | 2.2.1   | Background Information on Graph Theory 12                              |  |  |

|           |                        | 2.2.2   | Synchronous Circuits Represented as Graphs 13                          |  |  |

|           | 2.3                    | Clock   | ing of the Synchronous Circuits                                        |  |  |

|           | 2.4                    | Formu   | ulation of the Synchronous Circuit Optimization                        |  |  |

|           |                        | Proble  | em                                                                     |  |  |

|           |                        | 2.4.1   | Timing Constraints                                                     |  |  |

|           |                        |         | 2.4.1.1 Edge Weight Constraints                                        |  |  |

|           |                        |         | 2.4.1.2 Long Path Constraints 20                                       |  |  |

|           |                        |         | 2.4.1.3 Short Path Constraints 21                                      |  |  |

|           |                        |         | 2.4.1.4 Vertex Lags                                                    |  |  |

|           |                        | 2.4.2   | Linear Programming                                                     |  |  |

|           | 2.5                    | Algori  | ithms for Synchronous Circuit Optimization 24                          |  |  |

|           |                        | 2.5.1   | Notation for Algorithmic Complexity 24                                 |  |  |

|           |                        | 2.5.2   | Topological Sort                                                       |  |  |

|           |                        | 2.5.3   | Shortest Paths                                                         |  |  |

|           |                        |         | 2.5.3.1 Single Source Shortest Paths 29                                |  |  |

|           |                        |         | 2.5.3.2 All Pairs Shortest Paths                                       |  |  |

|           |                        |         | 2.5.3.3 Floyd-Warshall Method 30                                       |  |  |

|           |                        |         | 2.5.3.4 The Bellman-Ford Algorithm                                     |  |  |

|           |                        |         | 2.5.3.4.1 Relaxation                                                   |  |  |

|           |                        |         | 2.5.3.4.2 Using Bellman-Ford to Solve the Single-Source Shortest Paths |  |  |

|           |                        |         | Problem                                                                |  |  |

|           |                        |         | 2.5.3.4.3 Using Bellman-Ford to Solve Linear Programs                  |  |  |

|           |                        | 2.5.4   | Branch and Bound Algorithms 40                                         |  |  |

| Chapter 3 | Sync  | hronous   | VLSI Circuit Optimization Techniques                             | 43 |

|-----------|-------|-----------|------------------------------------------------------------------|----|

|           | 3.1   | Pipeli    | ning of Synchronous Digital Systems                              | 44 |

|           |       | 3.1.1     | Pipelining of Combinatorial Circuits                             | 44 |

|           |       | 3.1.2     | Pipelining of Microprocessors                                    | 47 |

|           |       | 3.1.3     | Pipelining of DSPs                                               | 49 |

|           |       | 3.1.4     | Wave-Pipelining                                                  | 50 |

|           | 3.2   | Retim     | ing Techniques for Sequential Circuit Optimization               | 51 |

|           |       | 3.2.1     | Overview of the Retiming Process                                 | 52 |

|           |       | 3.2.2     | More Recent Work in the Field of Retiming                        | 57 |

| Chapter 4 | Regis | ster Elec | trical Characteristics (RECs)                                    | 60 |

|           | 4.1   | The I     | mportance of an Effective Timing Model                           | 61 |

|           | 4.2   | Regis     | ter Delays                                                       | 63 |

|           |       | 4.2.1     | $T_{Set-up}$ , $T_{Hold}$ , $T_{C \rightarrow Q}$ , and $T_{CD}$ | 63 |

|           |       | 4.2.2     | Estimating $T_{Set-up}$ , $T_{Hold}$ , and $T_{C \rightarrow Q}$ | 66 |

|           |       | 4.2.3     | Estimating T <sub>CD</sub> from the Layout                       | 69 |

|           | 4.3   | Interc    | onnect Delays                                                    | 72 |

|           |       | 4.3.1     | $T_{Int1}$ and $T_{Int2}$                                        | 72 |

|           |       | 4.3.2     | T <sub>Int</sub> Calculated from the Layout                      | 73 |

|           |       | 4.3.3     | Load-Dependant Model for Interconnect Delays                     | 76 |

|           | 4.4   | Non-I     | deal Logic and Register Delays                                   | 77 |

|           |       | 4.4.1     | Model of Logic Delay                                             | 79 |

|           |       | 4.4.2     | Model of Non-Uniform Logic Element Delays                        | 80 |

|           | 4.5   | Mode      | ling the RECs                                                    | 83 |

|           |       | 4.5.1     | Basic REC Model (Level 1)                                        | 83 |

|           |       | 4.5.2     | The Enhanced REC Model (Level 2)                                 | 86 |

|           | 4.6   | Path I    | Delays                                                           | 89 |

|           |       | 4.6.1     | Path Delays using REC Level 1 Model                              | 91 |

|           |       | 4.6.2     | Path Delays using REC Level 2 Model                              | 94 |

|           |       | 4.6.3     | Short Paths                                                      | 97 |

|           |       | 4.6.4     | Internal Short and Long Paths                                    | 97 |

| Chapter 5 | Retin | ning with | h RECs                                                                                   | 99  |

|-----------|-------|-----------|------------------------------------------------------------------------------------------|-----|

|           | 5.1   | Incorp    | porating REC's into the Retiming Process                                                 | 103 |

|           | 5.2   | Seque     | ntial Adjacency Matrix (SAM)                                                             | 107 |

|           | 5.3   | Timin     | g Constraints                                                                            | 109 |

|           |       | 5.3.1     | Negative edge weight constraints                                                         | 110 |

|           |       | 5.3.2     | Long path constraints                                                                    | 110 |

|           |       | 5.3.3     | Short path constraints                                                                   | 112 |

|           |       | 5.3.4     | Internal path constraints                                                                | 112 |

|           |       | 5.3.5     | Constraints due to vertex lags                                                           | 115 |

|           | 5.4   | Retim     | ing Algorithm                                                                            | 116 |

|           |       | 5.4.1     | RETSAM: Retiming Algorithm for Synchronous Circuits with Attached Electrical Information | 117 |

|           |       | 5.4.2     | CHECKCP: Clock Period Feasibility Check                                                  | 118 |

|           |       | 5.4.3     | SOLVELAGS: Determination of the Vertex Lags Using a Branch and Bound Approach            | 119 |

|           | 5.5   | Path I    | Delay Monotonicity Constraints                                                           | 125 |

|           |       | 5.5.1     | Intuition for the Monotonicity Constraints                                               | 126 |

|           |       | 5.5.2     | Designing the Clock Distribution Network                                                 | 129 |

|           |       | 5.5.3     | Feasibility Check for the Clock Distribution Network                                     | 132 |

|           |       | 5.5.4     | Derivation of the Monotonicity Constraints                                               | 134 |

|           | 5.6   | Exper     | imental Results                                                                          | 140 |

|           |       | 5.6.1     | Application of RETSAM to Modified MCNC Benchmark Circuits                                | 140 |

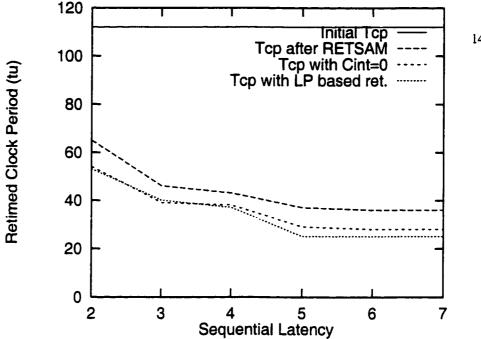

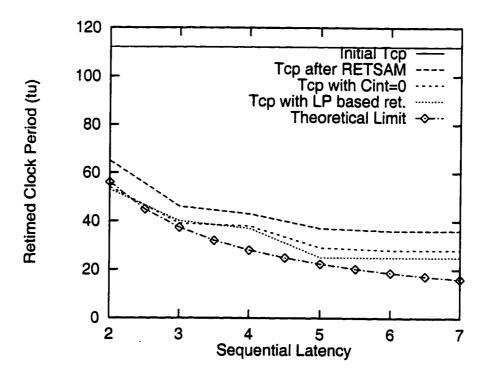

|           |       | 5.6.2     | The Impact of Latency on the Retimed Clock Period                                        | 144 |

|           | 5.7   | Concl     | usions                                                                                   | 147 |

| Chapter 6    | Conclu  | sions .   |                                                              | 150 |

|--------------|---------|-----------|--------------------------------------------------------------|-----|

| Chapter 7    | Future  | Work .    |                                                              | 154 |

| ·            | 7.1     | -         | ng the Impact of Pipelining Depth on Retimed um Clock Period | 156 |

|              | 7.2     |           | ing Recursive DSP Circuit Architectures                      |     |

|              |         | 7.2.1     | Theoretical Background on IIR Filter                         |     |

|              |         |           | Characterization                                             | 160 |

|              |         | 7.2.2     | Clustered Look-Ahead Pipelining                              | 161 |

|              |         | 7.2.3     | Scattered Look-Ahead Pipelining                              | 162 |

|              |         | 7.2.4     | Minimum Denominator Multiplier (MDM)                         | 164 |

| Bibliography |         | · • • • • |                                                              | 166 |

| Annendix A   | Publica | itions .  |                                                              | 175 |

## LIST OF TABLES

| <u>Table</u> | <u>Title</u>                                                                                                                                                                                    | Page         |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| i            | Delay of a 1 bit adder for different input and output pairs usin 5 V CMOS technology. Note the non-uniformity due to asymlogic paths within the adder                                           | metry in the |

| 2            | Delay of a 4-bit adder for different input and output pairs using V CMOS technology. "x" denotes the delays that cannot be me a change at the specified input is not propagated to the specific | asured since |

| 3            | The SAM for the graph of Figure 33. Light shaded entries repaths, whereas dark shaded entries represent long paths for curve Unshaded entries denote permissible paths.                         | = 37 tu.     |

| 4            | Example solution for $c = 24$ . A single value is shown for equal upper bounds                                                                                                                  |              |

| 5            | Results of the application of the retiming algorithm to MCNC circuits                                                                                                                           |              |

# LIST OF FIGURES

| Figure | <u>Title</u> <u>Page</u>                                                                                                                                                                                                                                                |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

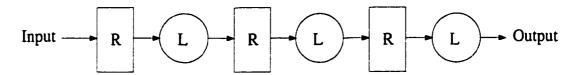

| ī      | A synchronous circuit with three registers. Data signals are moved from the input to the output at a constant rate (the clock period). Registers are indicated as "R," and the logic elements are indicated as "L." 8                                                   |

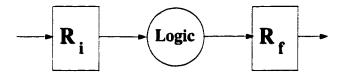

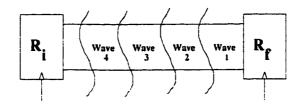

| 2      | Two sequentially adjacent registers (initial register $R_i$ and final register $R_f$ ) together with the logic elements between the two registers. This path forms a local data path                                                                                    |

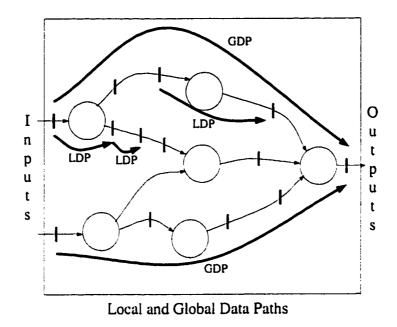

| 3      | A synchronous circuit with two inputs and a single output. Some local data paths (LDP) and global data paths (GDP) are indicated on the circuit. Registers are indicated with a vertical bar along the edges 11                                                         |

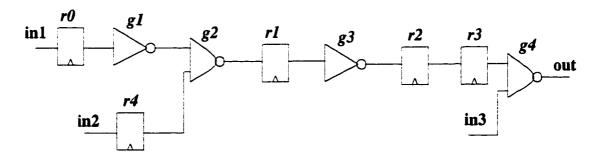

| 4      | A synchronous circuit with four logic gates (g1 through g4) and five synchronizing registers (r0 through r4)                                                                                                                                                            |

| 5      | A simple graph with an edge set $E$ and a vertex set $V$                                                                                                                                                                                                                |

| 6      | The graph representation of Figure 4. Vertices are used to represent the logic elements and edges are used to represent the connection between the logic elements. Note the use of zero delay vertices to model the inputs and outputs of the circuit                   |

| 7      | Due to the difference between the arrival time of the clock signal at the initial register $(C_i)$ and at the final register $(C_f)$ , negative and positive clock skew is created between the registers depending on the lead/lag relationship between $C_i$ and $C_f$ |

| 8      | Pseudocode of the Algorithm TS for the topological sort of a graph $G$ 26                                                                                                                                                                                               |

| 9      | Pseudocode of the algorithm VISIT for coloring every vertex in $G$ recursively                                                                                                                                                                                          |

| 10     | Pseudocode of the Floyd-Warshall algorithm                                                                                                                                                                                                                              |

| 11     | The relaxation procedure. (a) a tighter bound is found after relaxation, (b) relaxation has no effect                                                                                                                                                                   |

| 12 | Pseudocode of $RELAX(e)$ . $d[v]$ is updated according to the aforementioned procedure                                                                                                                                                                                                                                                                                                                                                                       |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

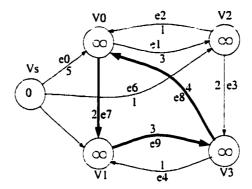

| 13 | An example graph which does not contain a negative cycle 37                                                                                                                                                                                                                                                                                                                                                                                                  |

| 14 | Graph of Figure 13 with a negative cycle along the path $v_0 \rightarrow v_1 \rightarrow v_3 \rightarrow v_0$ . Note that the negative edge weight of $e_8$ causes the negative cycle 37                                                                                                                                                                                                                                                                     |

| 15 | Pseudocode of the Bellman-Ford algorithm                                                                                                                                                                                                                                                                                                                                                                                                                     |

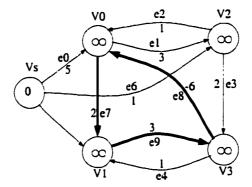

| 16 | Pipelining breaks global data paths into local data paths with smaller delay so as to increase the data flow rate                                                                                                                                                                                                                                                                                                                                            |

| 17 | Pipelining of microprocessors: five primary operations of the microprocessor are pipelined to increase computational speed 48                                                                                                                                                                                                                                                                                                                                |

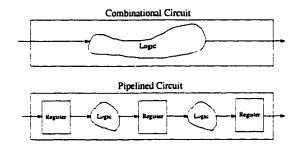

| 18 | In wave-pipelining, successive data waves propagate through the logic elements, forming an effective pipeline                                                                                                                                                                                                                                                                                                                                                |

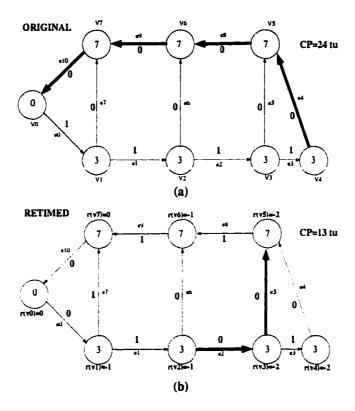

| 19 | a) The original graph introduced in and b) its retimed version. Note that the sequential latency is four clock periods in both cases. $r(v_n)$ denotes the lag of vertex $n$ after retiming                                                                                                                                                                                                                                                                  |

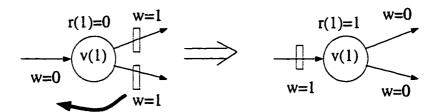

| 20 | The lag function changes the edge weights while preserving the circuit function. Increasing the lag of a vertex by one has the effect of increasing the weights of all edges by one connected in front of this vertex and decreasing the weights of all edges by one connected behind this vertex 56                                                                                                                                                         |

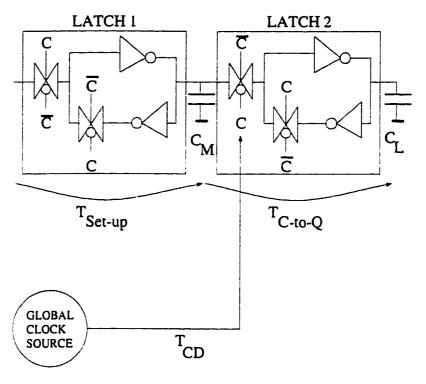

| 21 | A typical edge-triggered master-slave flip flop is composed of two latches. The set-up time is the time required for the data to successfully latch into the first latch. The hold time is the duration during which the data at the input of the register must be stable after the arrival of the clock signal. The clock-to-Q time is the time required for the data to appear at the output of the flip flop upon arrival of the incoming clock signal 64 |

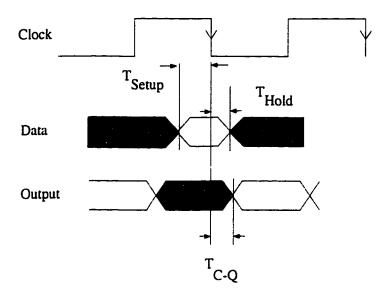

| 22 | Timing diagrams of the flip-flop shown in Figure 21. The data signal must be stable for $T_{Setup}$ before and $T_{Hold}$ after the arrival of the clock signal. The valid data signal appears at the output of the flip flop $T_{Clock-to-Q}$ after the clock signal arrives                                                                                                                                                                                |

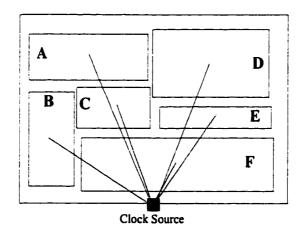

| 23 | A block diagram of an example integrated circuit layout. The chip area is assumed to be partitioned into regions of similar clock delay                                                                                                                                                                                                                                                                                                                      |

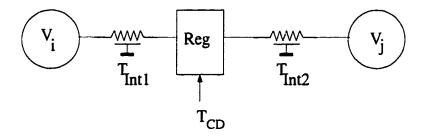

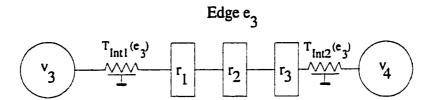

| 24 | The pre-register and post-register interconnect delays are caused by the distributed RC impedance of the connections between the register and the logic elements                                                                                                                |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

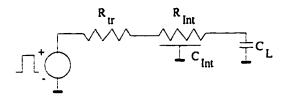

| 25 | A logic stage (or a register) connected to another logic stage or register through an interconnect. The 50% interconnect delay $T_{Int}$ caused by the RC impedance of the interconnect and the load capacitance is calculated based on physical parameters of the interconnect |

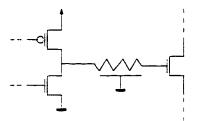

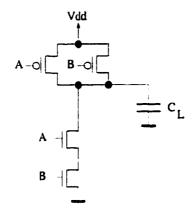

| 26 | A CMOS NAND gate. Note that the delay of this element is dependent on the output load. The element has an output slope $m$ characterizing this load dependence                                                                                                                  |

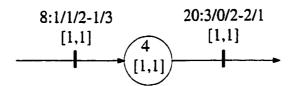

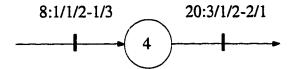

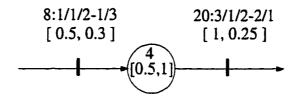

| 27 | A path containing two edges and a vertex between the two edges. The REC values are attached to each edge to characterize the registers, interconnect, and the clock delays located along the edges 85                                                                           |

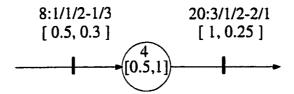

| 28 | The graph of Figure 27 with attached load dependent parameters. The values in the brackets are the enhanced REC values $m$ and $c$ 87                                                                                                                                           |

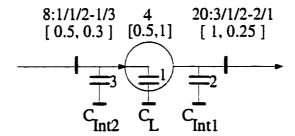

| 29 | $C_{Int2}$ and $C_L$ are the loads at the output of the initial register. The circle is the logic element (or vertex) with a delay of 4 tu, and load dependent $m$ and $c$ values of 0.5 and 1, respectively                                                                    |

| 30 | The path shown in Figure 27. The minimum and maximum path delays, $T_{PD_{min}}$ , and $T_{PD_{max}}$ between the two edges are calculated using (4.27) 93                                                                                                                      |

| 31 | The path shown in Figure 28. The path delay $T_{PD}$ between the two edges is calculated from (4.30)                                                                                                                                                                            |

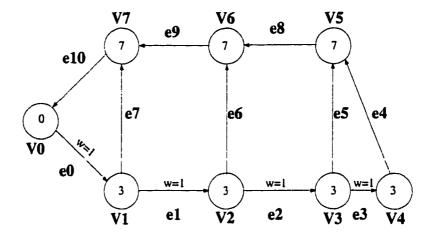

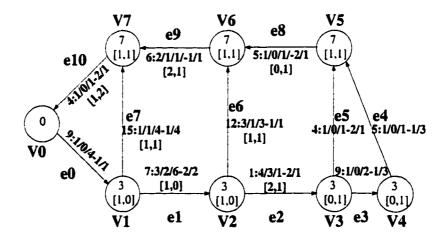

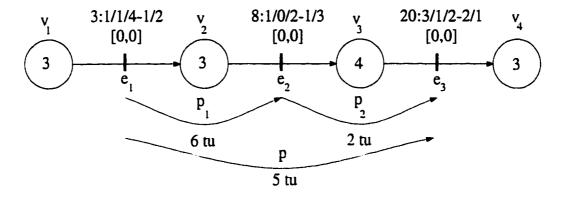

| 32 | Graph of the digital correlator in . The edges that are not labeled are assumed to have zero weight                                                                                                                                                                             |

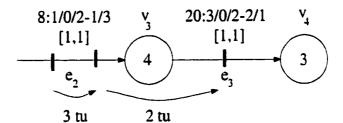

| 33 | Graph of the digital correlator with added REC values. The edges that do not have $[m, c]$ values assigned are assumed to have values $m = 0$ and $c = 0$                                                                                                                       |

| 34 | The internal path delay between registers located on the same edge, $T_{PD_{Internal_{max}}}$ , is equal due to the definition of the RECs. This example demonstrates the case where $w(e_3) = 3. \dots 114$                                                                    |

| 35 | An example graph in which the internal path delay on edge $e_2$ exceeds the path delay between $e_2$ and $e_3$ . This graph exemplifies the importance of considering internal long paths before the retiming process is initiated 114                                                                                                                                                                         |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 36 | Pseudo-code for RETSAM                                                                                                                                                                                                                                                                                                                                                                                         |

| 37 | Pseudo-code for clock period feasibility test, CHECKCP 119                                                                                                                                                                                                                                                                                                                                                     |

| 38 | Pseudo-code for the branch and bound algorithm SOLVELAGS that calculates the vertex lags                                                                                                                                                                                                                                                                                                                       |

| 39 | An example graph in which the path delays do not monotonically increase. The sub-path $p_1$ has a delay greater than its original path $p$ . The cause of this non-monotonic behavior is due to the negative clock skew between edges $e_1$ and $e_2$ . Note that only the maximum path delay, $T_{PD_{max}}$ , is considered and the load-dependence of the delays is assumed to be negligible for simplicity |

| 40 | Pseudo-code version of algorithm for designing the clock distribution network                                                                                                                                                                                                                                                                                                                                  |

| 41 | A path p with 3 registers and 2 vertices                                                                                                                                                                                                                                                                                                                                                                       |

| 42 | A path containing two registers and a vertex between the two registers. The path delay $T_{PD}$ contains components related to the register delays. If all registers in the circuit are similar, the register delay components would be equal                                                                                                                                                                  |

| 43 | Effect of the pipelining depth on the clock period on C17. The initial clock period is 112 tu which is shown as a solid line 147                                                                                                                                                                                                                                                                               |

| 44 | The theoretical limit from Figure 43. Note that the effect of negative clock skew is ignored                                                                                                                                                                                                                                                                                                                   |

## Chapter 1. Introduction

Digital circuits perform tasks by logical functions. The speed at which these logical operations can be completed is defined by the delays of the logic elements used in the digital circuits such as inverters, OR gates, and AND gates. A digital circuit containing one or multiple levels of logic elements is called a **combinational** circuit. Alternatively, in a **synchronous** circuit, synchronizing elements called **flip flops** or **registers** are used to ensure that data signals reach specified destinations at specified times. These synchronizing elements permit the realization of complex digital functions which are sequentially ordered.

The concept of inserting flip flops into a circuit in order to divide the main circuit function into isolated sub-functions was first proposed by Cotten in [1]. The sub-functions are performed independently of each other by placing the logic elements between the flip flops. The result of one sub-function is held at the input of the corresponding register and upon arrival of the next clock signal, transferred to the output of that register. Therefore, provided that a certain function can be divided into n independent sub-functions, the overall processing speed of the system can be increased by a factor of n by using n-1 flip flops. This technique is called **pipelining**.

A revised version of the same technique called **maximum-rate pipelining** was first proposed in [2], also by Cotten. In this technique, multiple data signals are fed into the input of a circuit during the same clock cycle such that these signals travel

simultaneously from one register to the next without overriding each other. This process of transmitting multiple *waves* of data signals permits operating at a higher data rate than is possible with conventional pipelining. This technique requires careful consideration of the data skew, specifically the difference between the *minimum* delays and the *maximum* delays between the registers, since data-overwriting could occur. This technique is called **wave pipelining** [3, 4]. In wave pipelining, the capacitance in the logic elements is used to temporarily store the values of the data waves. Typically, wave-pipelined systems can operate at three to seven times the frequency of a similar pipelined system. The limiting factor for the speed of a wave pipelined system is the *differences* between the different path delays, since the number of waves that are possible is limited by the uncertainities in the path delays [3] caused by process parameter variations [4].

Pipelining of recursive structures such as digital IIR filters has been studied in [5–9]. The inherent difficulty in pipelining recursive digital filters is due to the delay of the feedback loop built into these architectures [10]. Three different compensation techniques are introduced to handle the feedback [9–11]. The primary goal of pipelining a synchronous system is to increase the operation speed of the system. Similarly, the purpose of pipelining a recursive digital filter is to increase the sampling frequency of the filter. The application of algorithms to increase the sampling frequency of a digital filter is discussed in this dissertation.

Although pipelining offers significant performance advantages, this technique increases the latency of the synchronous circuit (the number of clock cycles required for

a data signal to reach the output of the circuit). A technique to increase the speed of a synchronous circuit without changing the latency was first proposed by Leiserson and Saxe in [12]. This technique, called **retiming**, relocates the flip flops in a synchronous circuit so as to increase the speed of the synchronous circuit by changing the relative location of the registers. The number of clock periods required to traverse every path between the input and the output is preserved, *i.e.*, the overall input-to-output latency of the synchronous circuit remains the same once this operation is completed [13, 14]. This technique therefore improves the synchronous speed without changing the latency while preserving the system function. Advanced techniques to increase the accuracy of retiming by incorporating low-level circuit issues are proposed in [15–17].

The aforementioned techniques exploit parallelism both in time and in space. In pipelining, parallelism in time is exploited by inserting the pipelining registers so as to permit parallel execution of multiple functions at the same time. Since each register is responsible for completing an independent subtask of a larger task, the results can be accomplished in parallel. This concept is similar to using multiple functional elements to perform multiple operations at the same time, thereby exploiting parallelism in space. Although early work in both pipelining and retiming permits automating the pipelining of VLSI circuits, accurate application of these techniques is not possible without considering low-level circuit details.

Incorporating low-level circuit parameters such as clock skew, interconnect delay, and variable register delays has been the focus of recent research. Early researchers [12]

have assumed equal register delays to model the effects of the registers. Equal register delays, however, have no impact on the optimization process since simple biasing of the clock period by the register delay value is sufficient to calculate the new clock period of the synchronous circuit [18]. Incorporating *variable* register delays, however, requires the redesign of existing algorithms and was first introduced in [19] along with variable interconnect delays. This approach was also extended by adding the effects of load-dependent delay [20, 21]. Incorporating clock skew is the first attempt to make retiming into a more practical optimization technique [19, 22–25]. Proposed research in this field includes optimizing multi-phase synchronous circuits [17, 26–29] as well as combining retiming with clock scheduling [30, 31]. Research in this field later has evolved to include the effects of precharged gate delays [32], multiplexers [33, 34], and relocating the registers so as to reduce the switching activity, thereby resulting in lower power consumption [35].

Automating the pipelining and retiming of VLSI circuits by considering the aforementioned low-level circuit details forms the basis of this dissertation. Without considering these low-level circuit characteristics, a useful optimization of a synchronous circuit is not feasible. The results obtained by omitting these effects may make the circuit implementation completely invalid. Therefore, this dissertation focuses on accurately automating the VLSI synchronous circuit optimization process without neglecting these crucially important circuit parameters.

This dissertation is organized as follows: In Chapter 2, background information

pertaining to the later chapters is provided. Terms that are used throughout this dissertation are introduced, and some common algorithms that form the basis of the algorithms that are developed in the following chapters are described. In Chapter 3, the aforementioned synchronous optimization techniques are introduced. A review of pipelining and retiming techniques is provided in this chapter. The model developed to include low-level circuit issues in synchronous optimization algorithms is introduced and described in Chapter 4. Based on the algorithms introduced in Chapter 2 and the timing model introduced in Chapter 4, new algorithms are developed that utilize this improved timing model. These retiming algorithms based on the enhanced timing model in Chapter 4 are described in Chapter 5. Some conclusions pertaining to the algorithms and techniques introduced in this research are drawn in Chapter 6. A discusion related to open-ended future research is provided in Chapter 7.

## Chapter 2. Theoretical Background

The primary objective of this dissertation is to introduce algorithms and design techniques that both consider and exploit low-level circuit information, such as the delays of the circuit building blocks including the effects of interconnect impedances. A synchronous circuit can be represented by a graph. The primary building blocks of a synchronous circuit are therefore represented by the vertices and edges of the graph. Values are assigned to the vertices and edges of the graph to characterize the components of the synchronous circuit being modeled by the graph. Using this modeling, existing graph-theoretical algorithms can be used for synchronous circuit optimization. Low-level circuit characteristics are integrated into a circuit model and previously developed algorithms to increase the accuracy of these existing algorithms.

In this chapter, a theoretical background is provided to introduce the key elements of this research. In Section 2.1, the terms related to synchronous circuits and used throughout this dissertation are introduced. The process of representing a synchronous circuit by a graph and some background information related to graph theory is described in Section 2.2. Due to its importance to this research, Section 2.3 is devoted to issues associated with the clocking of synchronous circuits. In Section 2.4, key issues related to converting a graph representation to a set of mathematical inequalities is described. Finally, the algorithms that are used to optimize the synchronous circuit are reviewed in Section 2.5.

## 2.1. Terms Related to Synchronous Circuits

A synchronous digital circuit consists of logic elements and storage elements (also called registers or memory elements) between these logic elements as shown in Figure 1. Synchronous circuits typically operate by clocking all registers in a circuit simultaneously. The logic elements located between the registers perform subtasks of the main system function. At the beginning of each clock interval, a different subtask is initiated by the logic subcircuit located at the output of each register. Each suboperation must be completed before the next clock signal is applied [1]. The temporal distance between the adjacent clock signals (called the **clock period** of the synchronous circuit) defines the rate at which new operations are performed. At each clock signal, the results of the completed subtasks are transferred to the next logic operation, and the following subtask is initiated. A synchronous circuit containing three registers is shown in Figure 1. Data signals are moved from the input of the circuit to its output at a rate defined by the clock frequency of the circuit. With this strategy, logic elements located at the output of different registers can work on different subtasks at the same time, thereby permitting a significant enhancement of the amount of information that can be processed concurrently by a synchronous circuit [1, 36].

Figure 1. A synchronous circuit with three registers. Data signals are moved from the input to the output at a constant rate (the clock period). Registers are indicated as "R," and the logic elements are indicated as "L."

The latency of a circuit is broadly defined within the literature. For a combinatorial circuit, the latency of the circuit is defined as the *time* required for a signal to reach the system output after arriving at the system input. For synchronous systems, however, this definition may be extended. For a synchronous system, two different latencies may be defined: **temporal latency**, the *time* required for a signal to reach the system output after arriving at the system input, and **sequential latency**, the *number of clock periods* required for a data signal to reach the system output upon the data signal arriving at the system input. The difference between these two definitions can be significant, since sequential optimization operations often do not change the sequential latency, but do change the temporal latency. These definitions of latency are used herein in order to provide insight into different effects of sequential optimization on system latency [37].

The **clock frequency** of a sequential circuit is the rate at which new data flow into the system and appear at the output. The primary goal of sequential optimization is to increase the clock frequency or equivalently decrease the clock period, the reciprocal of the clock frequency. The relationship between clock period and latency depends upon the degree of pipelining as described in [38, 39].

In a synchronous digital circuit, clock signals are distributed across an integrated circuit over conducting wires, typically composed of metal. These metal wires have a distributed RC impedance which degrade the shape of the clock signals. Depending on the thickness and width of the wires and the distance of the connections distributing the clock signal, clock delays may vary throughout the circuit. Since the RC impedance cannot be made zero in practical circuits, differences among the delays from the global clock source to different points in the circuit cannot be eliminated, unless specific design techniques are utilized. Due to this attribute of clock distribution networks in sequential circuits [40], clock signals typically reach different points in the circuit at different times. Therefore, differences in delay exist between the arrival times of the clock signals at different registers.

The absolute delay of the clock signal from the global clock source to a specific register (or memory element) is the **clock delay** and is denoted as  $T_{CD}$ . The difference between the clock delay of any two registers is the **clock skew** between these registers, denoted as  $T_{Skew}$ . The notion of **localized clock skew** and its application to increasing the clock frequency within pipelined systems was first introduced by Friedman and Mulligan in [38]. They show that only clock skew between **sequentially adjacent registers** (registers that receive information at successive clock intervals and are either directly connected or connected by logic elements) is significant in pipelined systems.

Sequentially adjacent registers form a local data path (LDP). A local data path consists of two sequentially adjacent registers and logic elements between these registers,

Figure 2. Two sequentially adjacent registers (initial register  $R_i$  and final register  $R_f$ ) together with the logic elements between the two registers. This path forms a local data path.

as shown in Figure 2.  $R_i$  and  $R_f$  are the initial and final registers, respectively. The local data paths with the greatest delay are the **critical data paths**, whose delay defines the minimum clock period (and therefore the maximum clock frequency) of the circuit. To permit a sequential circuit to operate faster, the amount of logic placed between these registers must be decreased. However, the cost (in area) of the sequential circuit increases in this case due to the added overhead caused by the additional registers in the circuit. This trade-off between circuit area and circuit speed has been previously investigated in [41]. **Global data paths** (GDP) are those paths between any input and any output of a pipelined circuit. A synchronous circuit with two inputs and a single output is shown in Figure 3.

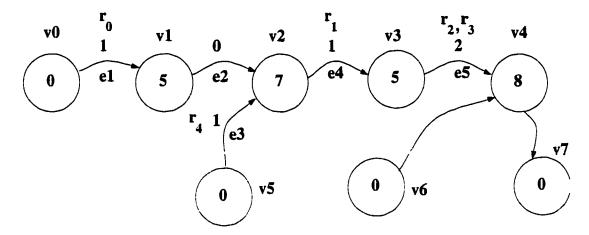

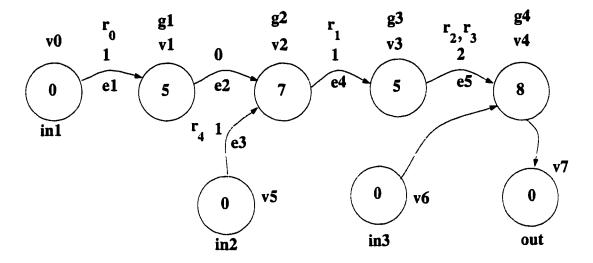

Note the aforementioned concept of adjacency between any two registers. The term that is defined here and plays a crucially important role in the following chapters is the sequential adjacency of a pair of registers. These two registers receive successive clock signals. Therefore, if a register receives a data signal at clock signal n, a sequentially adjacent register receives the processed data signal at a clock signal n + 1. For example, as shown in Figure 4, register pairs  $(r_0, r_1)$ ,  $(r_1, r_2)$ ,  $(r_4, r_1)$ , and  $(r_2, r_3)$  are sequentially

Figure 3. A synchronous circuit with two inputs and a single output. Some local data paths (LDP) and global data paths (GDP) are indicated on the circuit. Registers are indicated with a vertical bar along the edges.

adjacent, whereas register pairs  $(r_0, r_2)$ ,  $(r_4, r_2)$ ,  $(r_0, r_3)$ ,  $(r_4, r_3)$ , and  $(r_1, r_3)$  are not sequentially-adjacent.

Figure 4. A synchronous circuit with four logic gates (g1 through g4) and five synchronizing registers (r0 through r4).

## 2.2. Representing Synchronous Circuits Using Graphs

Synchronous circuits can be represented by graphs to permit the utilization of graph-theoretical approaches for synchronous optimization. In subsection 2.2.1, keywords that are borrowed from graph theory and used in this dissertation are introduced. The process of representing synchronous circuits using graphs is described in subsection 2.2.2. The material presented in this section permits using algorithms from graph theory to solve synchronous circuit optimization problems.

#### 2.2.1. Background Information on Graph Theory

A graph is a representation of a circuit, machine, or an event chain and is composed of an edge set E and a vertex set V. Cardinalities of these sets, |V| and |E|, denote the number of edges and vertices in the graph, respectively. A simple graph with seven vertices and seven edges is shown in Figure 5. The numbers inside the vertices and above the edges represent the vertex or edge **weight**, respectively. Depending on the application, this weight can be used to represent time, physical weight, length, etc. If, for example, the vertices are used to represent cities and the edges are used to represent highways between the cities, the edge weights can be used to represent the travel times along the highways and the cities can be used to represent the layover times inside the city terminals. A classical application of this type of representation is determining the shortest transition times between any pair of cities.

Figure 5. A simple graph with an edge set E and a vertex set V.

Every edge e has an initiating vertex and a terminating vertex. An edge that is initiated at vertex u and terminated at vertex v is represented as  $e: u \to v$ . To refer to these vertices without having to use different letters, the notations e.start and e.end are used in place of u and v.

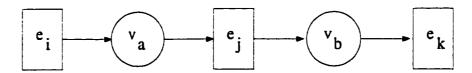

A path is a route between any pair of vertices or edges. A vertex-to-vertex path is a path that starts at a vertex u and ends at a vertex v and includes edges  $e_0$  through  $e_k$ . Such a path p is represented as  $p: u \to e_0 \to v_0 \to e_1 \to \ldots \to e_{k-1} \to v_{k-1} \to e_k$ , or simply  $p: u \leadsto v$ . An edge-to-edge path is represented in the same manner. For example, a path that starts at edge  $e_0$  and ends at edge  $e_k$  is represented as  $p: e_0 \leadsto e_k$ .

### 2.2.2. Synchronous Circuits Represented as Graphs

Synchronous circuits can be represented as graphs by using the vertices to represent the logic elements and the edges to represent the connection between a pair of logic elements. The edge weight is used to denote the number of registers between the logic elements and the numbers assigned to the vertices are used to denote the delay of the logic elements. The weight function  $w: E \to Z$  is defined to denote the weight of the edges. In the same manner, the delay function,  $d: V \to Z$  denotes the delay of the logic elements. For simplicity, it is assumed that the delay function is an integer, although the algorithms developed herein can be used with non-integer delays. The **path weight**, w(p), is defined as the sum of the weights of the edges along the path p. The **path delay**, d(p), is similarly defined as the sum of the delays of the logic elements along a path p.

Let p be a path with weight w(p) and delay d(p). The clock period of a synchronous circuit  $T_{CP}$  can be calculated as the greatest delay of any zero weight path in the circuit, as follows:

$$T_{CP} = \max\{d(p): w(p) = 0\}.$$

(2.1)

The path that has the greatest delay is called the **critical path** of the circuit. The rationale behind (2.1) and synchronous data flow in general is as follows: In a synchronous circuit, a data signal departing from a register must be provided sufficient time to arrive at the temporally farthest sequentially adjacent register. Otherwise the following clock signal will be applied before the data signal reaches the temporally farthest sequentially adjacent destination and is successfully latched, possibly overwriting an earlier data signal. Therefore, the temporal distance between the clock signals must be greater than

Figure 6. The graph representation of Figure 4. Vertices are used to represent the logic elements and edges are used to represent the connection between the logic elements.

Note the use of zero delay vertices to model the inputs and outputs of the circuit.

the longest delay between any sequentially adjacent register pair. Therefore, balancing the delays in a synchronous circuit yields a very efficient circuit since the number of logic blocks that are idle waiting for the next clock signal to arrive is minimized.

The graph representation of the synchronous circuit shown in Figure 4 is depicted in Figure 6. In Figure 6, the connections between the logic elements with no registers are modeled as zero weight edges and connections between the logic elements with registers are modeled as weighted edges. Zero delay vertices are used to represent the input and output nodes of the circuit.

## 2.3. Clocking of the Synchronous Circuits

The notion of sequential adjacency can be extended to edges. Sequentially adjacent

edges are those edges that receive data signals at successive clock signals. Only the last register of the initial edge and the first register of the terminating edge are sequentially adjacent. In Figure 6, the edge pairs  $(e_1, e_2)$  and  $(e_3, e_4)$  are sequentially adjacent, whereas the edge pairs  $(e_1, e_5)$  and  $(e_2, e_3)$  are not sequentially adjacent.

The clock skew  $T_{Skew}$  between two sequentially adjacent edges i and j is defined as

$$T_{Skew}(i,j) = T_{CD}(i) - T_{CD}(j),$$

(2.2)

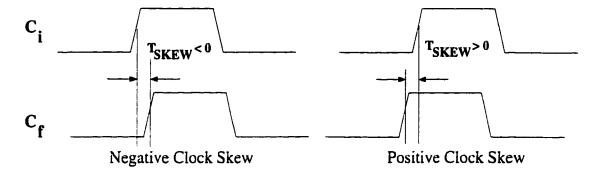

where  $T_{CD}(i)$  and  $T_{CD}(j)$  are the clock delays from the global clock source to nodes i and j. If  $T_{CD}(j) > T_{CD}(i)$ , the clock skew between registers i and j is defined as being negative. Negative clock skew occurs if the initial clock signal leads the final clock signal of a local data path. If  $T_{CD}(j) < T_{CD}(i)$ , the clock skew between registers i and j is positive. Positive clock skew occurs if the initial clock signal lags the final clock signal of a local data path. In the case that  $T_{CD}(j)$  equals  $T_{CD}(i)$ , i.e., the clock signal reaches the clock input of the two registers at precisely the same time, the clock skew is zero [42]. In Figure 7, it is shown how negative and positive clock skew can be created depending on the lead/lag relationship between the clock signals arriving at the initial and final registers of a local data path.

Figure 7. Due to the difference between the arrival time of the clock signal at the initial register  $(C_1)$  and at the final register  $(C_f)$ , negative and positive clock skew is created between the registers depending on the lead/lag relationship between  $C_1$  and  $C_f$ .

Positive clock skew increases the path delay of a local data path, potentially making its local data path a critical path, whereas negative clock skew may improve circuit speed in critical paths [42, 43]. However, negative clock skew may also create negative path delays, resulting in **race conditions**. Race conditions are caused by *early-clocking*, *i.e.*, clocking of registers before the relevant data is successfully latched. A race condition occurs if the skew is negative and greater in magnitude than the total local data path delay [38, 42, 43]. Those paths with negative delay are called **short paths** [44]. Similarly, a **long path** designates those paths with a delay greater than the desired clock period of the circuit.

# 2.4. Formulation of the Synchronous Circuit Optimization Problem

For a synchronous circuit to function properly, the clock period of the synchronous circuit must be greater than the delay of the critical data path of the circuit. Synchronous

optimization techniques permit the relocation or insertion of registers in the synchronous circuit so as to reduce the effective clock period. The critical path delay of the circuit may be reduced by placing a register within the critical path of the circuit. However, after inserting a register, one additional clock period is required to traverse the critical path, *i.e.*, the critical path is broken into two separate local data paths, each with smaller delay. Due to this added register, other registers may have to be removed from a related path so as not to increase the latency of the overall circuit. Removing registers from related paths may further change the latency and delay of these paths. Therefore, changing the location of one register may require a change in the entire circuit structure so as to preserve the original circuit function.

This complicated synchronous circuit optimization problem may be solved by applying linear programming methods. Local timing constraints are derived to ensure proper circuit operation. These constraints are converted to a set of linear inequalities permitting the application of standard linear programming techniques. These timing constraints are written to achieve a certain clock period by either keeping the latency constant or by increasing the latency. In the event that no satisfactory solution for the constraints is possible, the specified clock period cannot be achieved [14, 45].

# 2.4.1. Timing Constraints

Utilizing linear programming techniques for solving the synchronous circuit optimization problem is accomplished by formulating the synchronous optimization problem

as a linear program. The linear program consists of a set of timing constraints derived from each local data path of the synchronous circuit while achieving a specific clock period. The timing constraints are represented as the weight of the edges and the delay of the paths. The first set of constraints, the **edge weight constraints** [13, 23], is used to ensure that the weight of the edges are nonnegative after the optimization process has been completed. A second set of constraints, the **long path constraints** [14] and the **short path constraints** [23, 37], is used to ensure that the delay of each path in the circuit remains within a specified range. Vertex lags are introduced and used in this section to improve computational efficiency.

#### 2.4.1.1. Edge Weight Constraints

In the algorithms introduced in this dissertation, negative edge weights are not permitted. Negative edge weights are permitted temporarily for peripheral edges in [46] in order to shift the registers to the periphery of a synchronous circuit. This approach permits combinatorial optimization to be performed on the circuitry placed between the peripheral edges. However, since the algorithms described in this paper do not utilize this logic optimization feature, negative edge weights are disallowed. The negative edge weight constraint can be written as

$$w(e) \ge 0, \ \forall \ e \in E \ . \tag{2.3}$$

According to (2.3), all edge weights must have a zero or higher integer value. Edge weights are not permitted to be negative, even temporarily. This constraint ensures that

the edge weights are non-negative after completion of the synchronous optimization process without requiring additional optimization steps.

#### 2.4.1.2. Long Path Constraints

If a clock period C is desired, none of the zero weight paths in the synchronous circuit are permitted to have a delay that is more than C time units. Therefore, to ensure that a synchronous circuit has a clock period  $T_{CP} \leq C$ , paths with a path delay d(p) > C are disallowed. Assuming that the registers in the circuit have zero delay, the method used to eliminate an undesired path is to place a register along that path in order to make the path non-zero weight. Therefore, since the resulting path will have a higher weight, the path is divided into paths with less delay. For example, in Figure 6, the clock period is 12 time units (tu), since the critical path  $v1 \rightarrow v2$  has a delay of 12 tu. If a clock period of C = 10 tu is desired for this circuit, a register can be placed on edge  $e_2$ , thereby breaking this path into two smaller zero weight paths. This operation of inserting a register, however, changes the relative temporal nature of the circuit since the two inputs of  $v_2$  receive the data signals at different time intervals. To maintain the original circuit timing characteristics, a register may be placed on  $e_3$ , thereby delaying both inputs of  $v_2$  by the same number of clock periods. Although this process decreases the clock period of the circuit, it increases the sequential latency of the entire circuit since the global data paths  $v0 \rightarrow v7$  and  $v5 \rightarrow v7$  have a higher weight due to the added registers. The sequential optimization techniques presented in this dissertation fall

into the two separate categories of pipelining and retiming. Although both techniques are used to increase the overall system-wide clock frequency, pipelining increases the latency, whereas retiming preserves the original sequential latency.

For a path p consisting of multiple edges, the long path constraint is in the form of

$$w(p) > 0, \ \forall p: \ d(p) > c.$$

(2.4)

An interpretation of (2.4) is that a critical path p can be eliminated by making it non-zero weight, thereby dividing the path into multiple paths with smaller delay. It is important to note that (2.4) can be used to eliminate any *undesired* path, *i.e.*, not necessarily a path with a delay *greater* than desired. A path with a delay *lower* than desired can also be eliminated using the same process as described in the following subsection.

#### 2.4.1.3. Short Path Constraints

Short paths are created when the total delay of a path including the clock skew and register hold times is a zero or negative, thereby causing race conditions. Short path constraints can be modeled similarly to long path constraints. The notion of short paths plays a crucially important role in this dissertation and is investigated in great detail.

## 2.4.1.4. Vertex Lags

Observe that as the length of a path grows, the family of inequalities represented by (2.4) takes the form

$$w(e_0) + w(e_1) + \cdots + w(e_{k-2}) + w(e_{k-1}) > 0, \tag{2.5}$$

for a path consisting of k edges. However, Leiserson and Saxe show that by assigning an integer to each vertex, all of the inequalities that are represented by (2.4) can be transformed into a much simpler form [12–14]. The vertex lag function  $r: V \to Z$  is an integer vertex label which is defined as follows:

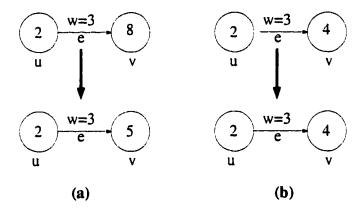

$$w'(e) = w(e) + r(v) - r(u), \tag{2.6}$$

where  $e: u \to v$  is an edge in the circuit with an initial weight of w(e) and a weight of w'(e) after completion of the synchronous circuit optimization. r(u) and r(v) are the vertex lags assigned to the vertices u and v. Using vertex lags for any path  $p: v_u \to v_b$  in the circuit, the following inequality holds:

$$w'(p) = w(p) + r(v_b) - r(v_a), \tag{2.7}$$

where w(p) and w'(p) are the initial and optimized path lengths and  $r(v_b)$  and  $r(v_a)$  are the vertex lags for the initial and the final vertices of path p.

Assume that path  $p: v_a \leadsto v_b$  has an initial weight of w(p) = 0 and p has a delay greater than a desired value c, i.e., d(p) > c. Therefore, path p can be made non-zero weight to eliminate that path. To make p non-zero weight, the following inequality is used,

$$w'(p) \ge 1. \tag{2.8}$$

or using vertex lags according to (2.7),

$$w(p) + r(v_b) - r(v_a) \ge 1 \implies r(v_a) - r(v_b) \le w(p) - 1. \tag{2.9}$$

The right hand side of this equation (w(p) - 1) consists of constants that are derived from the circuit, whereas the left hand side  $(r(v_a) - r(v_b))$  consists of unknowns that are solved to achieve synchronous circuit optimization. Writing a set of inequalities in the form of (2.9) and solving for these inequalities using linear programming techniques [47] forms the basis of most synchronous circuit optimization techniques described in this dissertation.

## 2.4.2. Linear Programming

The most common linear programming (LP) problem consists of solving the following set of equations [48]:

$$x_{1} - x_{2} \leq a_{12}$$

$$x_{3} - x_{4} \leq a_{34}$$

$$\vdots$$

$$x_{n-1} - x_{n} \leq a_{n-1n},$$

(2.10)

where  $x_1$  through  $x_n$  are unknowns and  $a_{12}$  through  $a_{n-1n}$  are constants.

The family of linear inequalities shown in (2.10) can be solved by a **Linear Program**. Standard synchronous optimization techniques consist of converting the aforementioned timing constraints into a linear program similar to (2.10), and applying a linear programming method such as the Bellman-Ford method. The Bellman-Ford method described in [47] is described in detail in the following subsection.

## 2.5. Algorithms for Synchronous Circuit Optimization

The building blocks for the algorithms introduced in this dissertation are topological sort, the Floyd-Warshall method, and the Bellman-Ford method. In subsection 2.5.1, the notation for describing the complexity of the algorithms used throughout the dissertation is introduced. The topological sort algorithm is introduced in subsection 2.5.2. The Floyd-Warshall and Bellman-Ford algorithm for determining shortest paths in a graph are introduced in subsection 2.5.3. These algorithms are used both in standard synchronous optimization algorithms [12–14] as well as the algorithms described in this dissertation.

In Section 2.5.4, the *branch and bound algorithms*, used to solve the generalized retiming problem, are introduced. These algorithms are used in those problems where the use of linear programming methods are not feasible. Branch-and-bound algorithms require excessive time, thereby making the application of these algorithms to large problem sets impractical. However, the properties of branch-and-bound algorithms is introduced for completeness. Readers with algorithms background can skip over this section.

# 2.5.1. Notation for Algorithmic Complexity

One of the more important attributes of an algorithm is its time-complexity, *i.e.*, the time requirement in relationship to its input size. The time-complexity of an algorithm is defined in terms of its asymptotic behavior. To clarify this concept, a simple algorithm that finds the maximum of n numbers can be considered as an example. In this example,

n numbers are processed, *i.e.*, the input size is n. If the input size doubles, the amount of time required for the algorithm to complete its processing is doubled. Thus, the operation time depends *linearly* on the input size. In this case the time-complexity of the algorithm is O(n).

Similarly, an algorithm that has a square time-dependence has a time-complexity of  $O(n^2)$ . An example is the bubble sort algorithm. Such an algorithm takes four times as long to complete when the input size doubles.

Although  $\Theta$  and  $\Omega$  notations of time-complexity exist for asymptotically tight and asymptotically lower bounds, respectively [49], only the asymptotically upper bound notation O() is used to denote time complexity in this dissertation.

#### 2.5.2. Topological Sort

Let G be a directed acyclic graph (DAG) whose vertices  $v_1$  through  $v_n$  represent the sub-events of a main event, and whose edges  $e_1$  through  $e_k$  define the order of occurence of these events. If event  $v_i$  occurs before event  $v_j$ , this behavior is represented by an edge from  $v_i$  to  $v_j$ . Topological sort is the process of ordering the vertices in such a way that if there is an edge from  $v_i$  to  $v_j$ ,  $v_i$  appears before  $v_j$  [49]. For a topological sort, G is assumed to be directed and acyclic. In this dissertation, only directed acyclic graphs are considered since DAGs are the only type of graphs that are encountered for the specific problems discussed in this dissertation.

- 1. Let S[] be the array of sorted vertices in G.

- 2. Let c[] be the array that stores the colors of vertices of G, V(G).

- 3. for  $\forall u \in V(G)$  do {

- 4. c[u] = WHITE

- 5. S[u] = nil

- 6. }

- 7. i = |V|

- 8. for  $\forall u \in V(G)$  do

- 9. if color[u] = WHITE then VISIT(u)

Figure 8. Pseudocode of the Algorithm TS for the topological sort of a graph G.

Topological sort utilizes a technique called a depth first search (DFS). In this subsection, the DFS algorithm is not separated from the topological sort. The pseudocode of the topological sort algorithm TS is shown in Figure 8. Algorithm TS plays an important role in the algorithms discussed later in this dissertation since the candidate paths are sorted using this algorithm, TS.

Algorithm TS uses two arrays S[] (Step 1), and c[] (Step 2) to store the sorted vertex indices, and the colors of the vertices, respectively. The status of the vertices are indicated using colors: WHITE indicates an unprocessed vertex, GRAY indicates a process that is being processed, and BLACK indicates a vertex whose processing is completed. The initialization phase of the algorithm (the **for** loop between steps 3 and 6) colors all vertices WHITE (Step 4), and clears the sorted index array S (Step